韩国科学院 & 三星 S.PKG:2.5D Chiplet封装直接液体射流冷却方案

来源 | Energy Conversion and Management

链接 | https://doi.org/10.1002/adma.202510988

01

背景介绍

随着人工智能(机器学习、大语言模型)应用普及,异质集成 Chiplet 封装需求激增,其核心挑战包括:

热负荷突破传统极限:热设计功率(TDP)预计超1kW,峰值热流密度超500 W/cm²,传统空冷完全失效;

热生成不均:逻辑芯片(允许最高 125℃)与高带宽内存(HBM,允许最高 85℃)热流密度差异大,易导致温差过大、性能下降甚至芯片分层;

现有方案局限:微通道冷却存在温差大、压降高问题,且多数研究聚焦单一工质(如仅单相或仅两相)或铜基测试平台,缺乏封装级单 / 两相工质对比及非均匀热场景验证。

02

成果掠影

近期,韩国科学技术院的Youngsuk Nam联合三星电子高级研究团队S.PKG实验室Jaechoon Kim团队针对 AI 驱动的高功率异质集成芯片封装热管理需求,通过2.5D 热测试载体(TTV) 实验评估了单相去离子水与两相 HFE-7100的直接液体射流冲击冷却性能;该冷却模块采用4×4射流阵列精准覆盖高功率逻辑芯片,并通过横向二次流冷却相邻存储区域,有效降低了压降。此外,在硅表面通过深反应离子刻蚀技术制备的微针肋结构,在泵送功率增幅极小的前提下,显著提升了单相与两相冷却模式的传热性能。单相水冷却展现出卓越的热性能,在1千瓦热负荷下仅需1.3瓦泵送功率即可将芯片温度维持在70℃以下,并实现最低0.032 K/W的结至流体热阻。相比之下,在入口温度高达45℃时,微针肋表面的两相射流冷却虽热阻比单相水冷高8.7%,但基于㶲损指标的能效评估显示其能效提升达78%。通过在实际2.5D芯粒封装上直接比较工质特性、运行参数与表面结构,本研究为基于热性能、能效与可靠性的冷却策略选择提供了指导。研究结果凸显了直接液体射流冲击与硅微针肋结构相结合的策略,可作为高功率异构集成封装的能效优化热管理方案。研究成果“High efficiency single and multi-phase direct liquid jet-impingement cooling for heterogeneous packaging”为题发表在《Energy Conversion and Management》。

03

图文导读

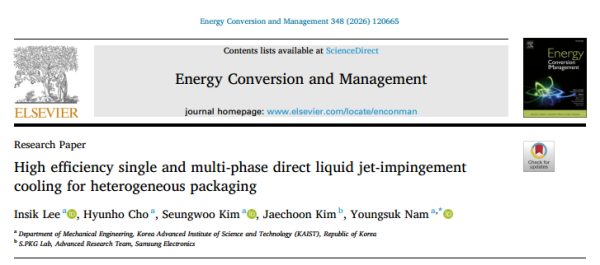

图1.(a)用于小芯片封装的单相和两相直接液体喷射冲击冷却的示意图。(b)具有单个逻辑芯片和六个HBM的目标2.5D半导体封装布局。(c)冷却2.5D封装TTV的喷射冷却模块的示意图。(d)相对于2.5D芯片布局的喷射喷嘴布置。

所选用的目标2.5D芯粒封装采用单逻辑芯片与六颗高带宽内存(HBM)的集成设计,其结构布局如图1(b)所示。这种构型实现了独特的冷却方案:高热通量区域通过具有较大流体动量的垂直射流冷却,低热通量区域则通过水平横流冷却,从而有望显著降低系统压降与泵送功耗。

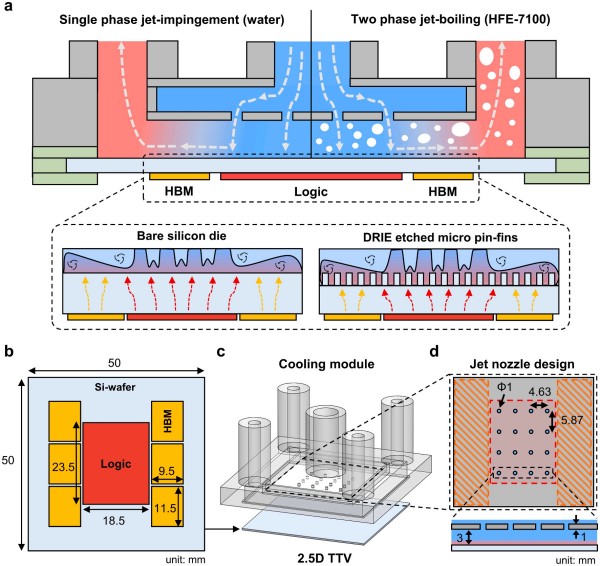

图2。(a)TTV制造工艺。(b)硅底部铂微加热器图案和硅顶部DRIE基微针鳍结构。(c)微针鳍阵列的共焦显微镜结果。

为模拟2.5D芯粒封装多热源的复杂发热场景,本研究开发了基于硅材料的热测试载体,其表面设有分别对应逻辑芯片与高带宽内存芯片的独立加热区域。图2展示了该制备流程,结构与加热区:硅基载体,含 1 个逻辑芯片加热区和 6 个 HBM 加热区,逻辑与 HBM 总功率比固定为7:3(如 1kW TDP 时,逻辑 700W、HBM 总 300W);表面改性:通过深反应离子刻蚀(DRIE) 制备微针翅结构,尺寸为:宽 50μm、间距 50μm、深 120μm,相比裸表面传热面积增加3.4 倍,且缩短冷却液与结区距离至≈600μm;测温优化:背面喷涂黑体涂层(发射率 0.95),配合 IR 相机精准测温。

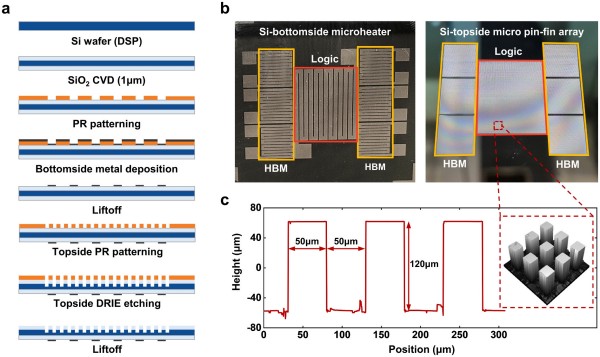

图3.(a)实验装置示意图。(b)试验段组件的分解图。(c)实验装置的照片。

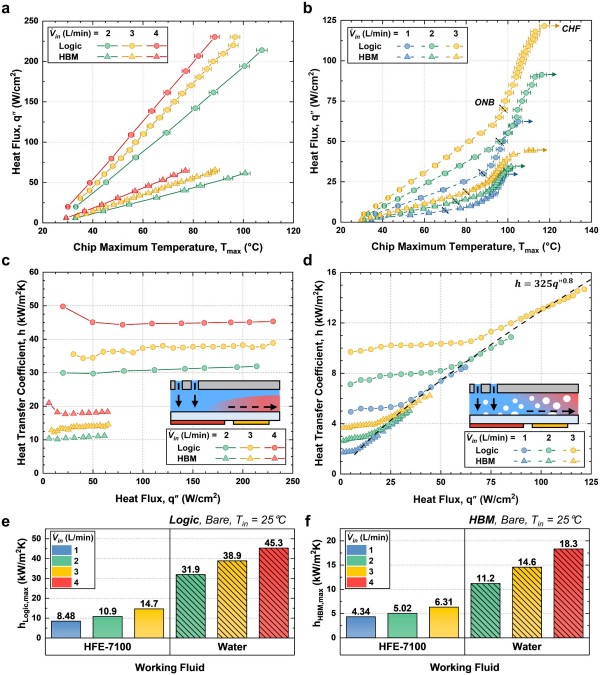

图4.(a)单相和(b)多相最大芯片温度变化与热通量的关系。(c)单相和(d)多相射流冲击传热系数变化与热通量的关系。(e)逻辑芯片和(f)HBM芯片的最大传热系数。

流量对单 / 两相冷却性能的影响——单相水冷却(图 4a、c):温度变化:热流密度增加时,芯片温度线性升高;流量从 2L/min 增至 4L/min,逻辑芯片最高温度显著降低(1kW 下从≈85℃降至 < 70℃);传热系数(HTC):HTC 随流量增加而升高,且逻辑芯片(射流直接冲击)HTC 显著高于 HBM(横流冷却),如 3L/min 流量下逻辑 HTC≈45.3 kW/m²・K,HBM≈14.7 kW/m²・K(图 4e、f)。

两相 HFE-7100 冷却(图 4b、d):传热阶段:分 “对流主导区”(< onset of boiling, ONB)和 “沸腾主导区”(>ONB);对流区温度随热流线性升高,沸腾区因相变潜热,温度增速放缓;CHF 变化:流量增加提升 CHF(3L/min 时 CHF 超 100W/cm²),且沸腾区不同流量的 HTC 收敛于拟合曲线h=325q''⁰·⁸(图 4d),表明沸腾主导传热时流量影响减弱;ONB 特征:逻辑芯片需更高过热度触发 ONB(3L/min 时需 28.8℃),HBM 仅需 9.6℃(图 5c),因射流区对流更强,抑制气泡成核。

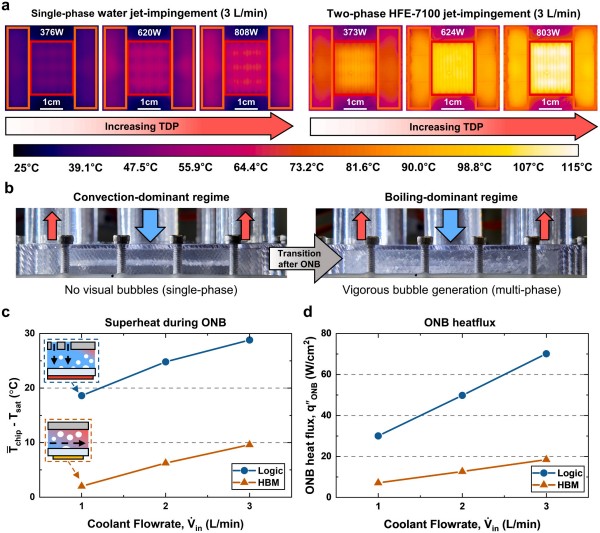

图5.(a)水和HFE-7100在不同TDP下的2.5D TTV IR温度场比较。(b)沸腾开始前后两相射流冲击冷却模块的侧视图。(c)过热和(d)取决于不同芯片区域冷却剂流速的沸腾开始所需的热通量。

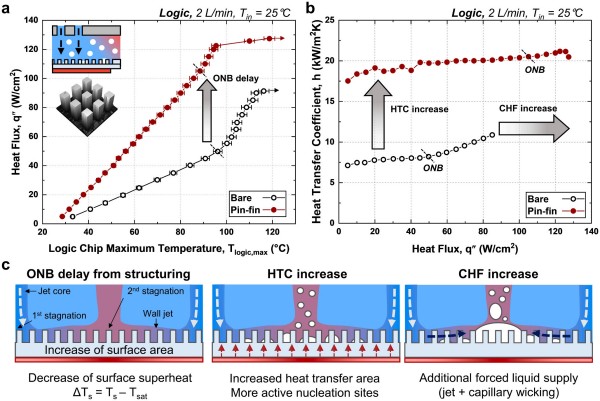

图6.(a)逻辑芯片热通量随逻辑芯片最高温度的变化(b)表面改性对传热系数和沸腾现象的影响(c)针翅对液体直接喷射沸腾传热影响的示意图。

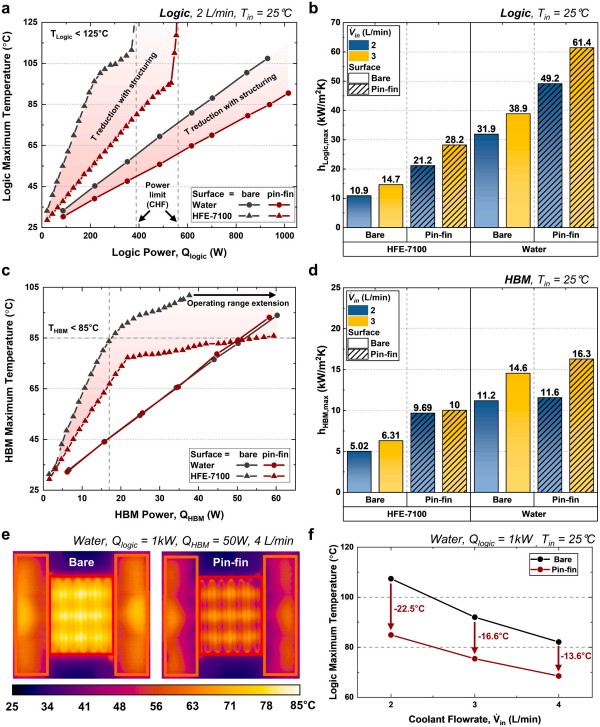

图7.(a)不同工作流体在不同流速下的逻辑芯片最高温度。(b)工作流体之间的逻辑HTC比较。(c)不同工作流体在不同流速下的HBM最高温度。(d)工作流体之间的HBM HTC比较。(e)最高功率条件下的IR温度图像。(f)通过表面结构化降低逻辑芯片最高温度。

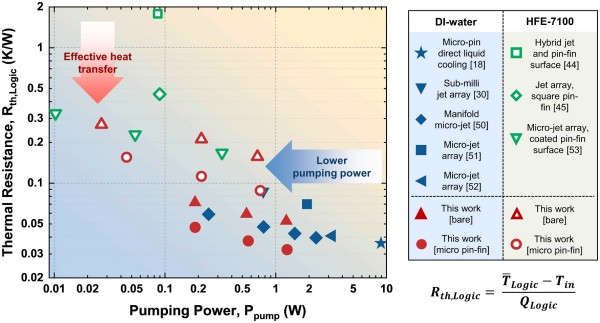

DRIE 微针翅结构的传热增强效果——单相冷却提升:温度降低:1kW 热负荷、2L/min 流量下,微针翅表面逻辑芯片温度比裸表面低22.5℃(图 7f);4L/min 流量下,实现最低0.032 K/W的结 - 液热阻,优于所有文献报道的单相水冷却结果(图 11);机制:增大传热面积 + 强化局部湍流,减少热边界层厚度。

两相冷却提升:CHF 提升:微针翅通过毛细芯吸增强液体补给,CHF 平均提升52%,最高达190.3 W/cm²(3L/min 流量,图 10b);沸腾优化:提供更多气泡成核位点,减少气泡滞留,ONB 过热度降低(图 S6),且沸腾区 HTC 显著高于裸表面(图 6b)。

泵功影响:微针翅仅导致压降轻微增加,泵功增幅可忽略(如 2L/min 流量下泵功仍 <0.2W),实现 “高效传热 + 低能耗” 平衡。

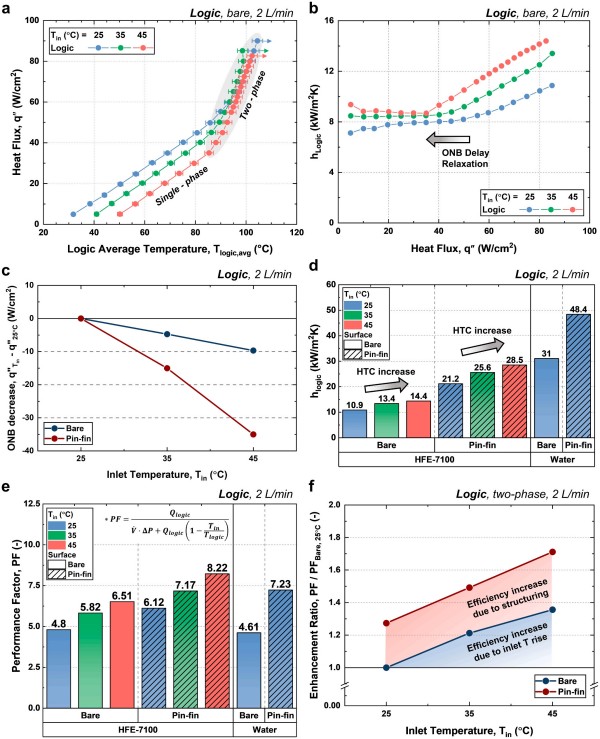

图8.(a)不同入口过冷度下的射流沸腾曲线。(B)不同入口温度下的HTC变化。(c)对于裸露表面和结构化表面,由于入口温度升高,ON B热通量降低。(d)取决于入口温度的不同表面上的最大HTC变化。(e)各种冷却条件下评估的能效性能因子。(f)由于入口温度升高和表面结构化而导致的性能系数增强比。

入口温度对能效与传热的优化——ONB 优化:入口温度从 25℃升至 45℃,微针翅表面的 ONB 热流密度从105 W/cm²降至70.1 W/cm²(图 8c),减少沸腾延迟,扩大两相运行窗口;

能效提升:基于火用损失的性能因子(PF)显示,入口温度每升高 10℃,能效提升16.2%(图 8f);45℃入口时,微针翅表面两相冷却的 PF 高于裸硅单相水(图 8e),且降低冷却回路热负荷(减少冷凝器能耗);

HTC 匹配:45℃入口时,微针翅表面两相 HFE-7100 的 HTC 接近裸硅单相水(图 8d),实现相近传热性能且更节能,为高入口温场景(如数据中心)提供方案。

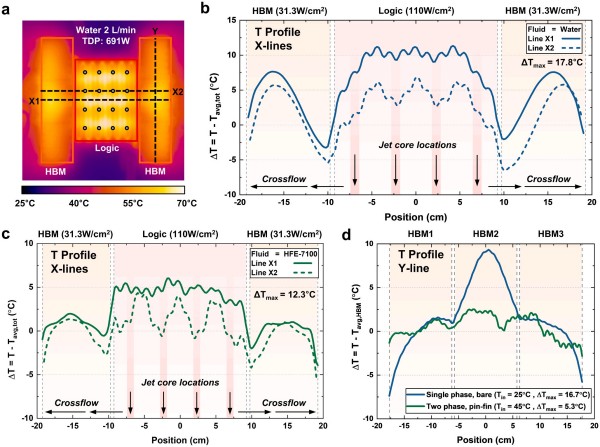

图9.(a)在红外温度图像上绘制的X和Y温度曲线。(b)单相水射流冷却(裸,2L/min,和Tin = 25 ℃)和(c)两相介电流体喷射冷却(针翅,2 L/min,和Tin = 45 ° C)温度均匀性,绘制在X线上,其中逻辑和HBM的热点都位于X线上。(d)每种冷却方式下HBM芯片之间的温度均匀性。

水平方向上的横流幅度进一步减弱,导致HBM之间的最大局部温度变化为16.7℃。另一方面,两相冷却在HBM之间提供了更均匀的温度分布,最大温差仅为5.4 ℃。当使用两相冷却剂时,横流大小的差异不太明显。

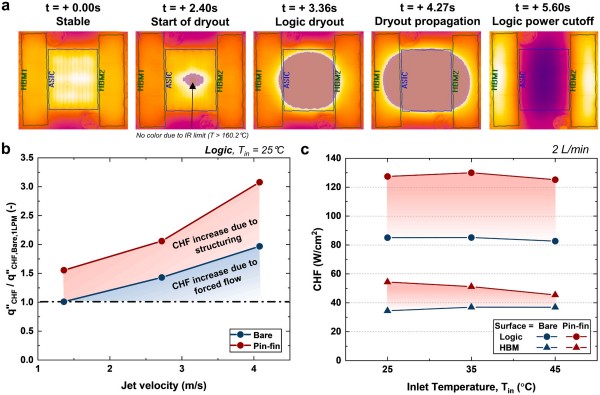

图10.(a)由于临界热通量(ASIC =逻辑区域)引起的2.5D TTV热失控的可视化。(b)射流冲击强制流和表面结构的CHF增强率。(c)入口温度升高引起的CHF变化。

温度均匀性与 CHF 失效机制——温度均匀性:逻辑芯片:单相水冷却温差14.9℃,两相冷却仅7.9℃(图 9b、c);HBM 区域:单相水冷却温差16.7℃,两相冷却仅5.4℃(图 9d);原因:两相沸腾主导传热,不受射流位置影响,而单相传热依赖射流 stagnation zone,易形成次级滞止区热点。

CHF 失效机制:失效起点:CHF 干烧从 “中央次级滞止区” 开始(射流相互作用形成的低流速区), vapor 膜快速扩散导致全表面干烧(图 10a);影响因素:流量增加→CHF 线性升高(液体补给增强),入口升温→CHF 降低(液体过冷度减小),如 25→45℃时裸表面 CHF 降2.4 W/cm²(图 10c)。

图11.各种参考文献和我们的工作建议的基于结平均温度与冷却模块泵浦功率的总热阻。

04

作者信息

Youngsuk Nam,韩国科学技术院副教授,研究方向:相变传热、热管理、热能、微/纳表面、数据驱动优化;主要研究成果:

基于液滴冲击的高功率超疏水热释电发电机

通过抑制多孔镓基相变材料过冷实现电子设备可持续热调控

被动式抗浸润超疏水表面

能源转换与管理

集成多孔金属基多尺度流道歧管的节能型电池热管理系统

具备自清洁能力的可扩展无眩光抗反射分级结构表面