普渡大学魏体伟,微射流液冷热流密度252 W/cm²刷新记录!

来源 | International Journal of Heat and Mass Transfer

链接 | https://doi.org/10.1016/j.ijheatmasstransfer.2025.126978

01

当AI芯片的热量冲上千瓦级

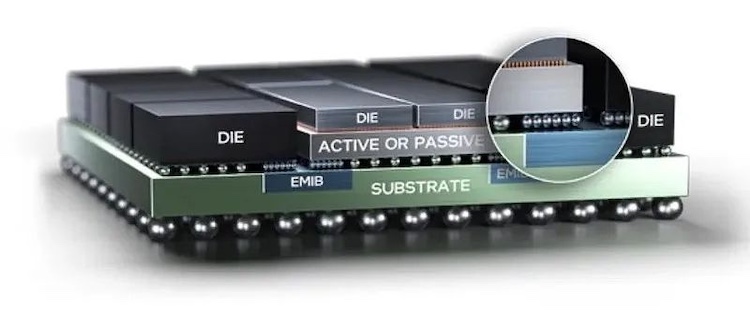

在人工智能、大语言模型、高性能计算(HPC)全面爆发的当下,芯片不仅变得更“聪明”,也变得越来越“烫”。尤其是用于 AI 加速的先进封装方案,如2.5D封装将多个高功耗计算芯片(如 GPU/ASIC/SoC)与高带宽存储(HBM)密集集成于一个封装平台之上。这种超高密度集成架构虽然极大提升了数据吞吐率与封装紧凑性,却也带来了前所未有的热管理挑战。

如:如何在紧凑封装中消除千瓦级热量?如何同时保证多个芯片温度不过热?尤其是逻辑芯片和HBM,这两个热敏感程度完全不同的器件,如何做到“各得其所”?

传统冷却手段(风冷、均温板、热管)早已难以胜任,哪怕是液冷冷板方案,在面对非均匀、多芯片、多热流密度的应用场景下,也捉襟见肘。

因此,研究者开始将目光投向一种更激进、更高效的冷却策略:微尺度液体射流冲击冷却(Microscale Jet Impingement Cooling)。这是一种以微喷嘴直接将冷却液高速射向芯片热源表面的技术,具有换热系数高、响应速度快、热阻极低等优势,被视为未来HPC芯片冷却的潜力选项之一。迄今为止,多数相关研究仍停留在单芯片验证,要真正让这项技术走向实用,还需要回答一个关键问题,多芯片能同时被液体射流精准冷却吗?

02

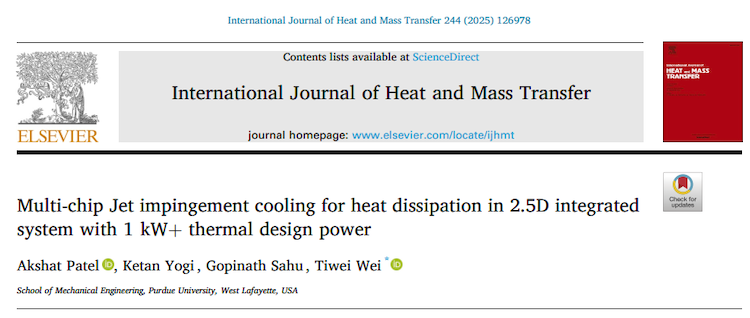

一次关于极限散热能力的系统验证

普渡大学魏体伟团队首次以1.86 kW热功率为设计目标,构建并实测了一种面向2.5D封装的多芯片微射流冷却原型系统,探索了串联流道布局下,逻辑芯片与四颗HBM在共享冷却器结构中的散热协同机制。该研究围绕高热通量下的2.5D多芯片封装冷却挑战,提出并验证了一种微尺度串联射流冷却器,可同时高效冷却逻辑芯片与多颗HBM,主要成果如下:实现总热设计功率 1.86 kW,其中逻辑芯片热流密度高达 252 W/cm²;逻辑芯片热阻低至 0.183 cm²·K/W,芯片间温差控制在 3°C 以内;串联流道设计显著提升了冷却液利用效率,相比并联系统具有更优的温控表现;实验结果与数值模拟高度吻合,验证了系统的设计合理性与工程可行性。这项工作为多芯片集成系统中的散热瓶颈提供了新思路与实证依据,特别适用于未来高性能AI加速器、GPU集群、HBM堆叠等极限散热场景。研究成果以“Multi-chip Jet impingement cooling for heat dissipation in 2.5D integrated system with 1 kW+ thermal design power”为题发表在《Multi-chip Jet impingement cooling for heat dissipation in 2.5D integrated system with 1 kW+ thermal design power》期刊。

03

图文导读

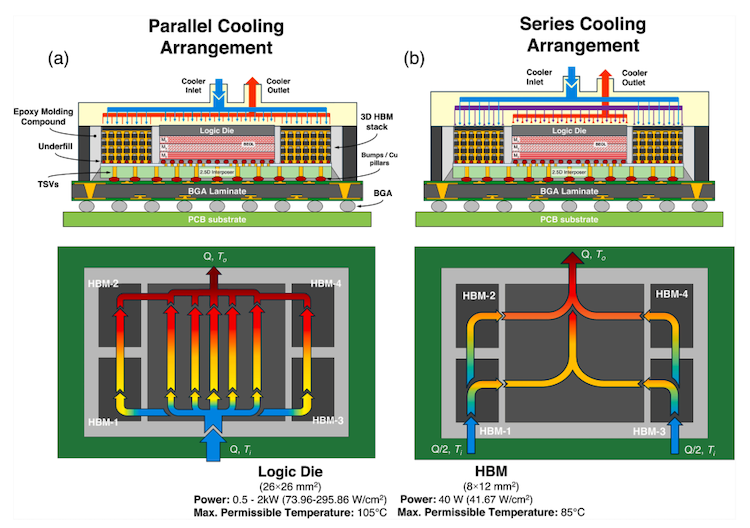

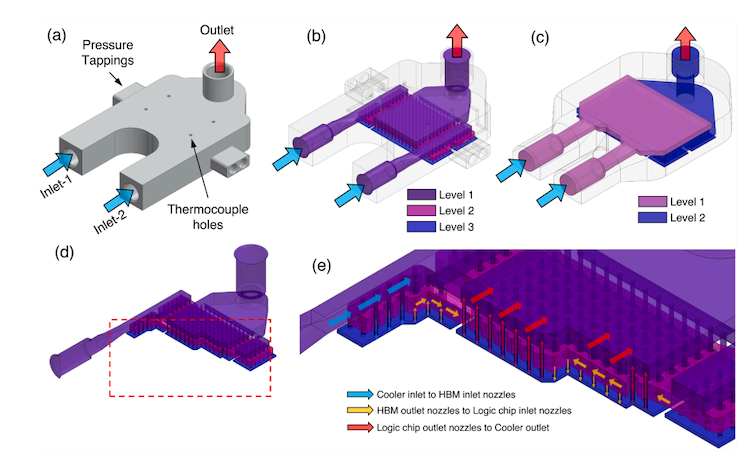

图1. 2.5D封装的微尺度射流冲击冷却装置,(a)并联冷却装置(b)串联冷却装置。

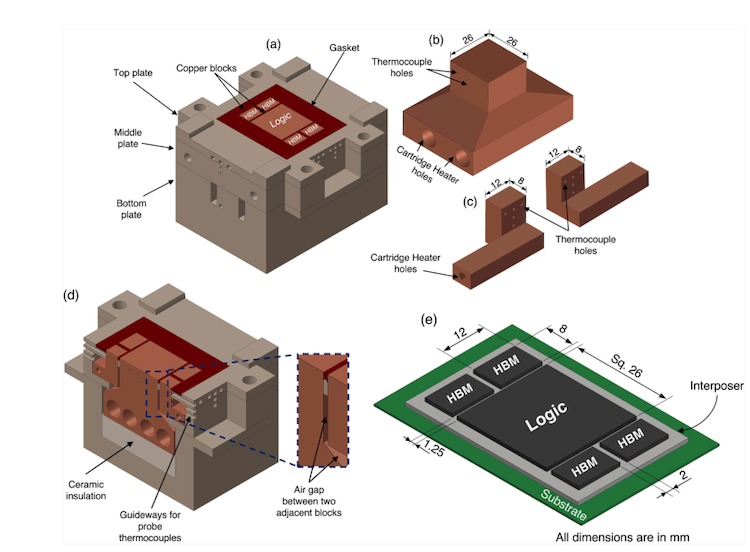

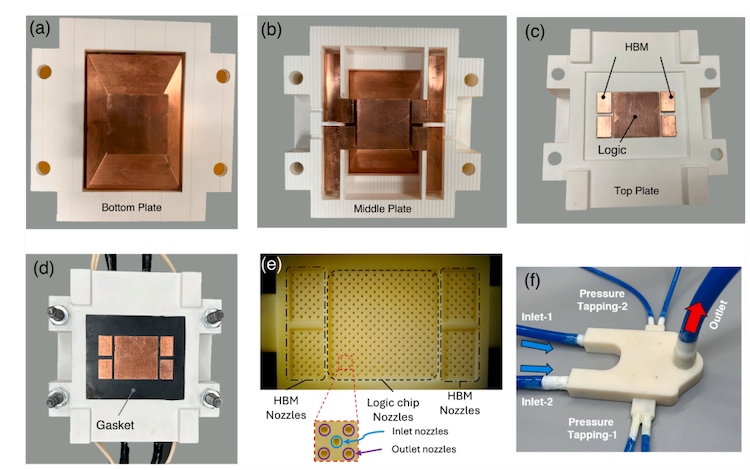

图2. (a) 三层外壳中的加热模块子组件,用于模拟HPC系统中的2.5D中介层封装;(b) 模拟逻辑芯片的加热模块;(c) 模拟HBM的加热模块;(d) 装配体的剖视图,突出内部结构;(e) HPC封装的实际芯片布局。

图 2d 和 2e 展示了实验中用于热源模拟的分层结构图和热流布置方式。

使用铝板和铜板堆叠,模拟真实2.5D封装中HBM和逻辑芯片的布局;

四颗HBM芯片分布在外围(每颗尺寸10 × 10 mm²,功率40 W),中间为逻辑芯片(20 × 20 mm²,功率变化范围126~252 W);

加热元件(heating elements)贴附于铜板下方,施加不同功率进行测试;

上层封装材料覆盖整个热区,实现均匀受热,尽量模拟真实芯片热扩散环境;

该结构不仅考虑了芯片功率密度,还重构了封装环境下的热扩散路径,有助于评估冷却器在真实多芯片结构中的控温能力。

图3. (a) 基于串联布置的微尺度射流冲击冷却器及其主要特征;(b) 串联冷却器的内部流体域(c) 并联冷却器的等效内部流体域;(d) 串联冷却器内部流体域的剖视图;(e) 放大剖面图,展示串联冷却器内部的流体流动路径。

该图展示了微射流冷却器的详细结构示意图,是本研究的设计核心。

冷却器采用串联式流动结构,冷却液从入口依次冲击4个HBM芯片,再汇集流向中心逻辑芯片;

共有4个射流入口通道(jet inlet channels)和1个主出口(main outlet);

射流喷口(jet nozzles)设计成阵列排布,每个芯片区域喷射孔布局对应其热源尺寸;

这种串联布局意味着冷却液在经过HBM芯片后温度会略升高,但集中射向逻辑芯片时仍具备足够的冷却能力,从而优先保障逻辑芯片这一高热流密度区的冷却需求,实现了结构上的“分级冷却”。

图4. (a) 底板中的逻辑芯片加热模块;(b) 中板中的HBM加热模块;(c) 顶板的放置以实现所需芯片布局;(d) 加热模块与外壳的组合装配(带密封垫);(e) 制造完成的微尺度射流冲击冷却器的喷嘴阵列;(f) 冷却器的多组进出液管道连接结构。

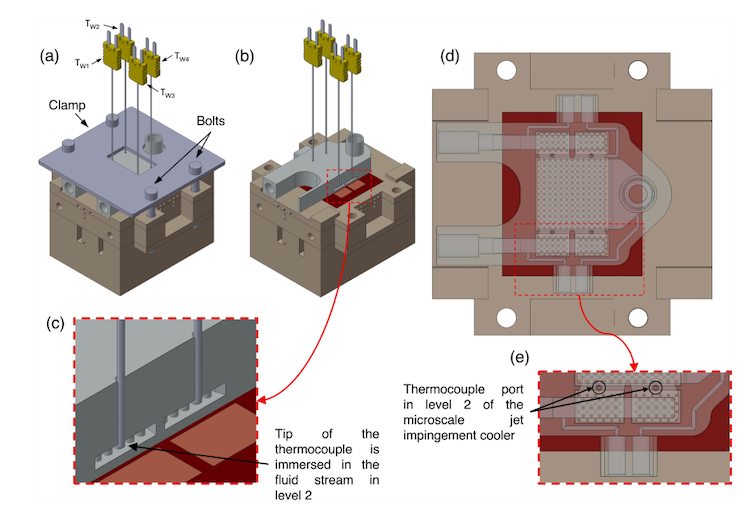

图5. (a) 加热-外壳子组件与微尺度射流冲击冷却器的整体组装图(含热电偶);(b) 冷却器的剖面图;(c) 剖面图的放大视图,突出热电偶的布置位置;(d) 整体装配的俯视图;(e) 装配放大图,突出热电偶接口的位置分布。

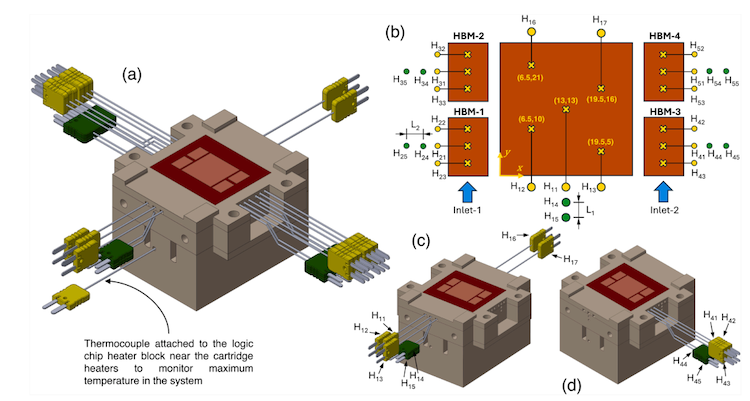

图6. (a) 安装热电偶的加热-外壳子组件;(b) 芯片布局上的传感器分布图示意图;(c) 安装逻辑芯片热电偶的子组件;(d) 安装HBM热电偶的子组件(图中仅示例展示HBM-3的热电偶)。

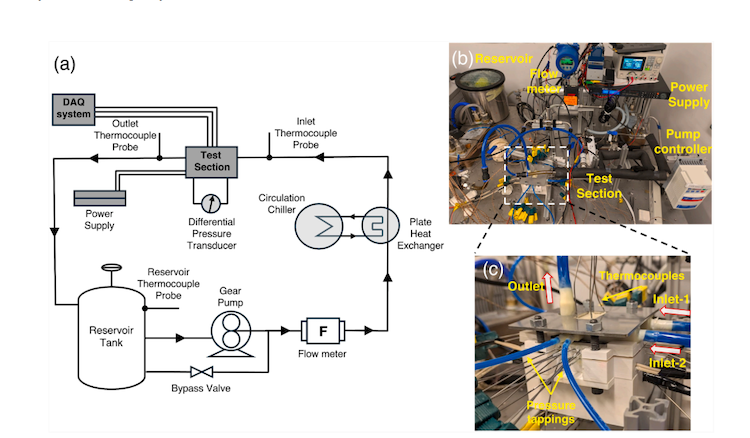

图7. (a) 流体循环系统示意图;(b) 实验测试中使用的流动回路系统;(c) 实验测试段照片。

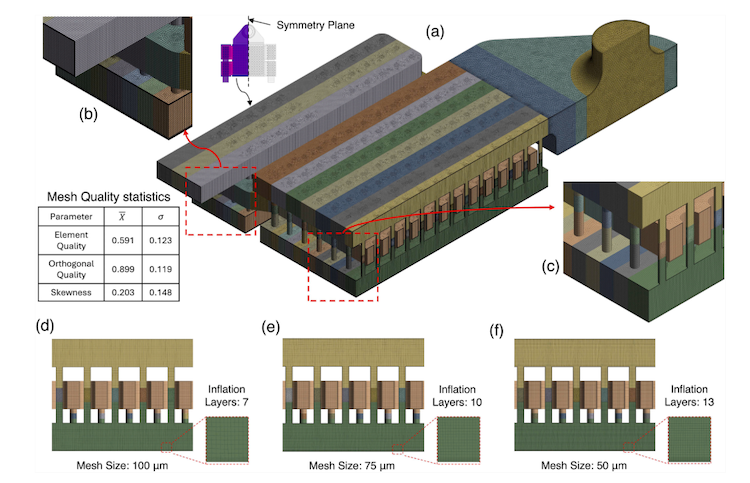

图8. (a) 冷却器一半区域用于数值模拟的整体网格;(b) HBM区域网格结构的放大图;(c) 逻辑芯片区域网格结构的放大图;(d) 网格尺寸为100 μm时的网格与膨胀层放大图;(e) 网格尺寸为75 μm时的网格与膨胀层放大图;(f) 网格尺寸为50 μm时的网格与膨胀层放大图。

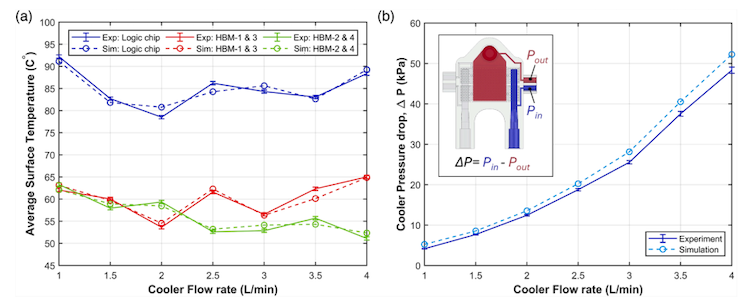

图9. (a) 逻辑芯片及所有HBM的平均表面温度:实验与模拟对比;(b) 冷却器压降:实验与模拟对比;

此图对比了逻辑芯片与HBM芯片的表面温度变化,横坐标为逻辑芯片热流密度(126–252 W/cm²)。

逻辑芯片温度随热流密度升高而上升,但在252 W/cm²时最高温度仍保持在105°C以内。

HBM芯片温度几乎保持恒定(<85°C),不受逻辑芯片升温影响。

数值模拟与实验结果高度吻合(误差<3%)。

证明串联射流结构具有出色的芯片温度隔离能力,即使在热流密度急剧上升情况下也不会引发HBM过热,适用于热敏感芯片与高功耗芯片共封场景。

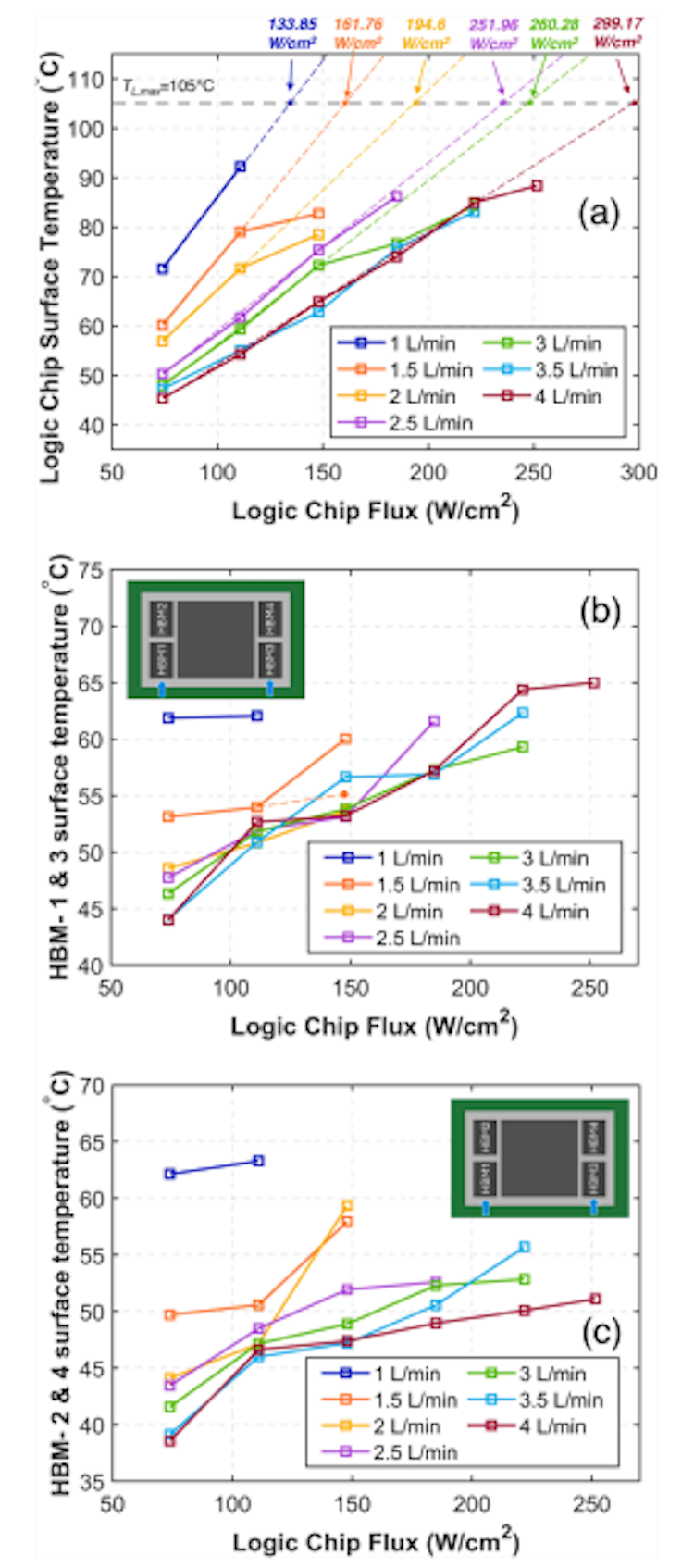

图10. 逻辑芯片热流密度对各芯片表面温度的影响:(a)逻辑芯片平均表面温度;(b)HBM 1 & 3 的平均表面温度;(c)HBM 2 & 4 的平均表面温度(HBM功率为40W,冷却器流速不同)。

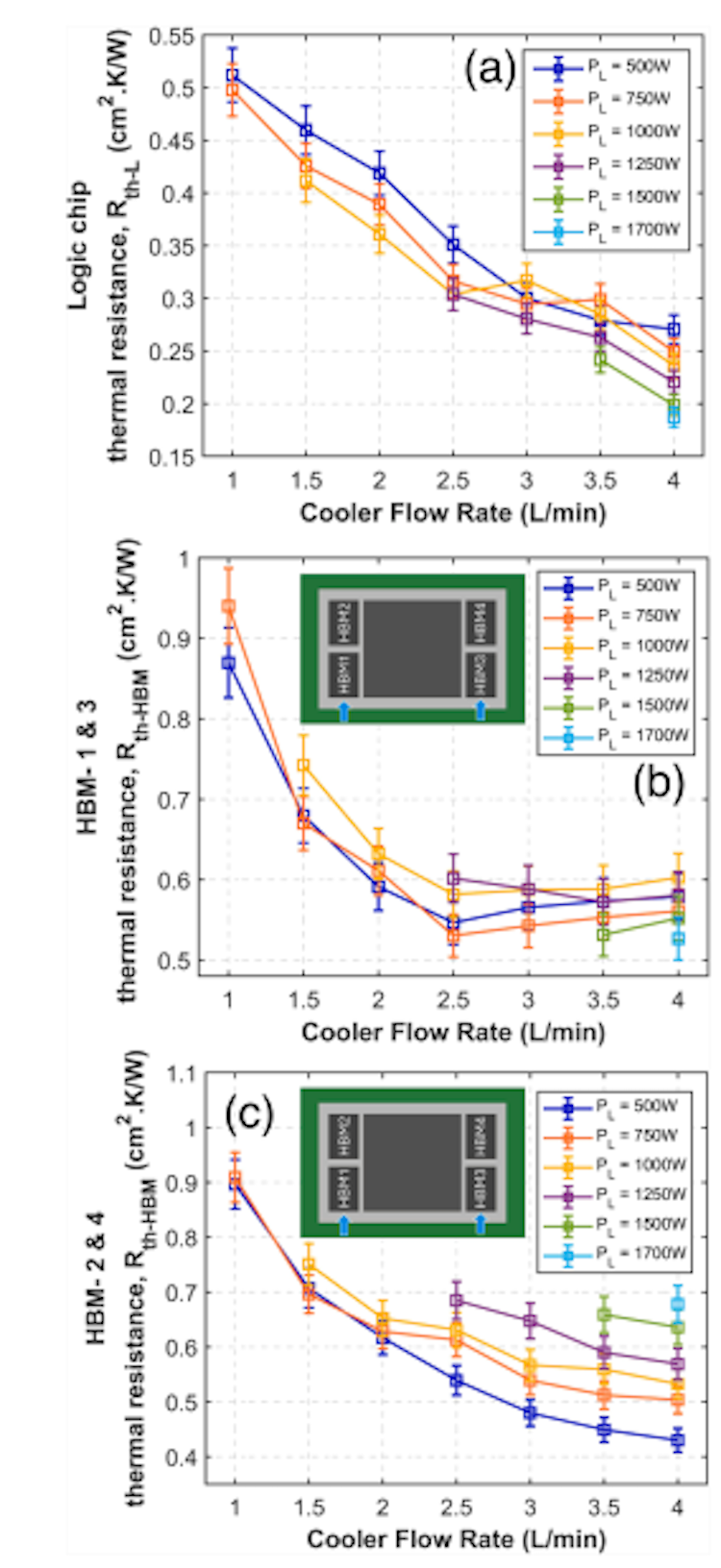

图11. 冷却流速对热阻的影响(a)逻辑芯片;(b)HBM1&3(c)HBM2&4(HBM功率为40W,逻辑芯片功率不同)。

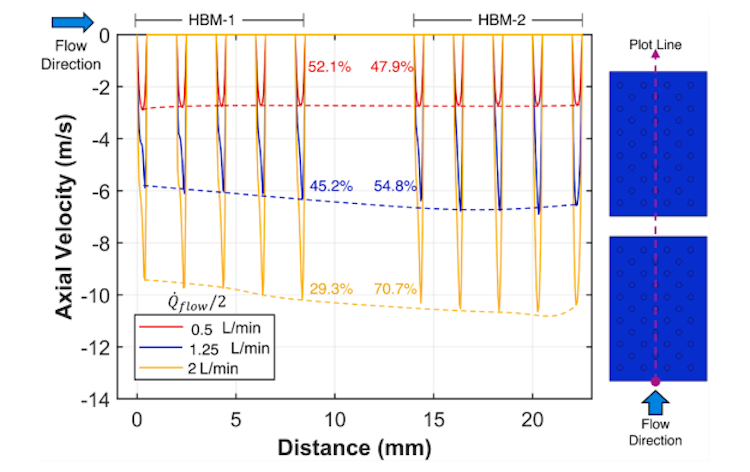

图12. HBM1与HBM2喷嘴出口处轴向速度分布的数值模拟结果(不同流速下),展示了流量分配及速度前沿的趋势线。

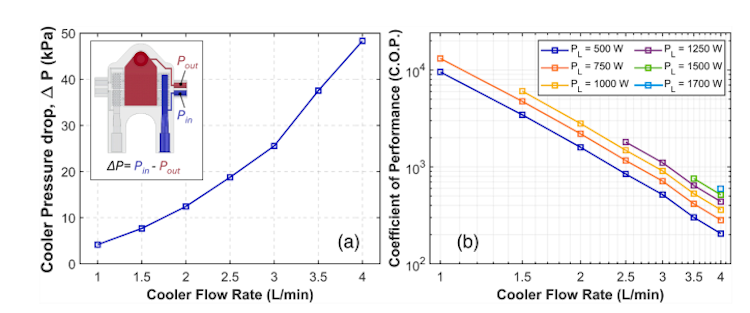

图13. 冷却器流速对:(a)压降;(b)性能系数(COP)的影响(HBM功率为40W,不同逻辑芯片功率)。

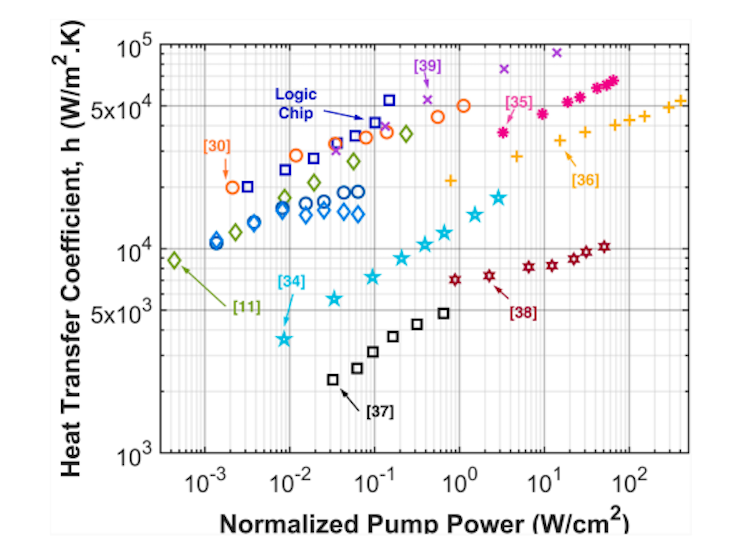

图14. 本研究冷却器与已有文献中其他冷却方案的热-流体性能对比。

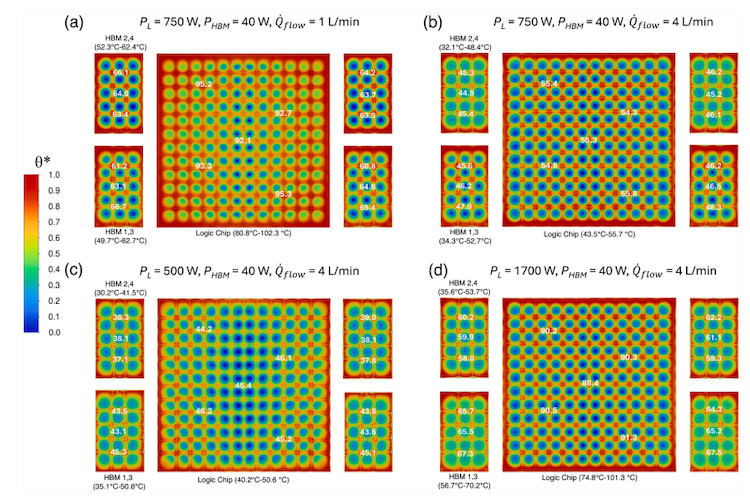

图15. 各工况下芯片表面的无量纲温度等值线图(数值模拟结果)。

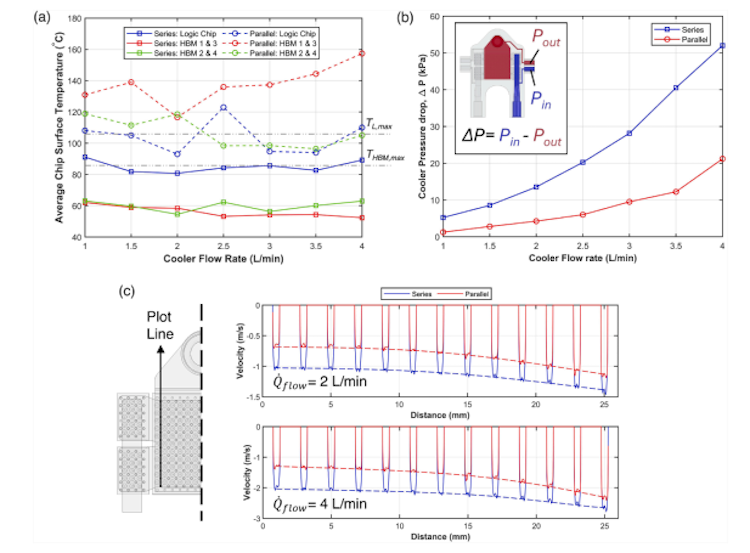

图16. 串联与并联结构的数值模拟结果比较:(a)芯片平均表面温度;(b)冷却器整体压降;(c)逻辑芯片喷嘴的轴向出口速度分布。

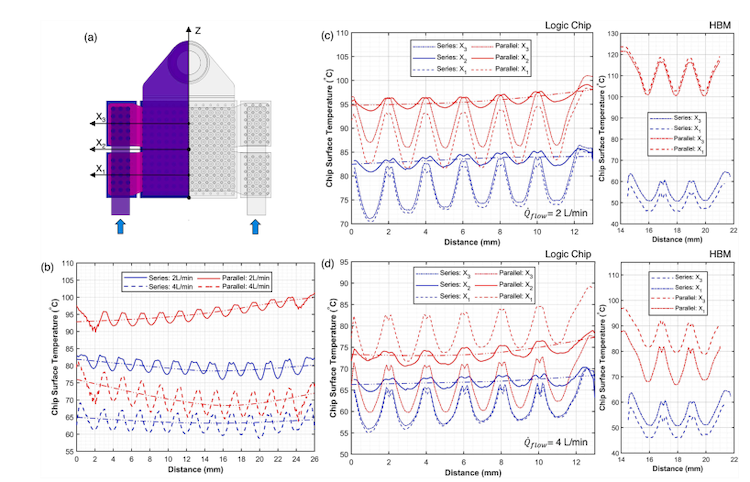

图17. (a) 冷却器示意图,标注各数据提取线;(b) 逻辑芯片表面沿Z线的温度分布;(c) 芯片表面沿X1、X2、X3线在2 L/min下的温度分布;(d) 在4 L/min下相同线路的温度分布。

随着2.5D/3D封装、HBM堆叠、高热流密度逻辑芯片等技术持续推进,传统“单芯片导热”范式正在被颠覆。热管理不再只是材料性能的比拼,更是系统级架构设计的协同优化。

魏体伟团队此次工作,用一套高度工程化的微射流冷却结构不仅刷新了实验室冷却能力的记录,也为异构集成、算力芯片封装的“散热未来”提供了现实解法。更重要的是,这套系统不是靠堆叠硬件指标赢得喝彩,而是从冷却路径、喷流结构、温控策略三个维度,构建了一个真正意义上的系统级散热范式。

如果你也在做芯片封装设计、液冷系统开发,或者正关注HPC/AI系统的散热痛点,那么这篇论文值得你认真读一读。

04

关于“魏体伟”

魏体伟是斯坦福大学机械工程系纳米传热研究组的博士后研究员,2020年博士毕业于欧洲微电子研究中心imec(全球著名微纳电子研发中心)和荷语鲁汶大学。魏博士将于2022年7月正式加入美国普渡大学机械工程学院担任助理教授,并组建Alpha Lab (All-in-one for Packaging, Heattransfer and Assembly Lab) 实验室,Alpha Lab的主要研究方向是芯片级三维系统集成,半导体互连和封装及芯片散热技术。

根据以上应用背景,AlphaLab的研究重点主要有以下几个方向:

三维系统集成(3D system integration), 包括新型三维集成堆叠技术,高密度互连技术;

芯片高性能冷却技术(Advanced thermal cooling),芯片级嵌入式微型沟道冷却和冲击射流冷却技术;

高性能散热材料开发与表征,包括高热导率热界面材料(thermal interface materials),高热导率底部填充材料(high thermal conductivity underfill)