下一代AI冷却:TSMC、Meta、HP、Google等迈向微通道液冷

00

引言

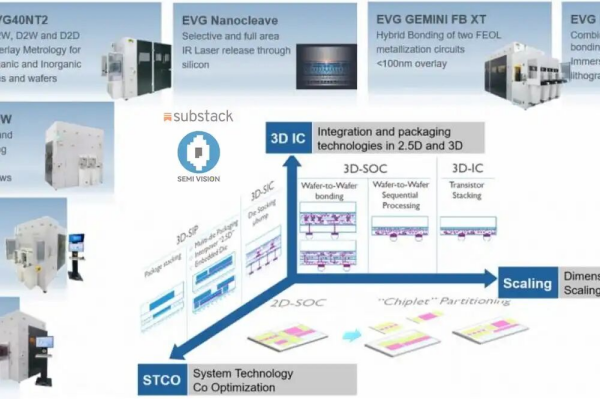

在2024年IEEE ECTC一篇题为 《Moving Towards Microchannel‑Based Chip Cooling(迈向基于微通道的芯片冷却)》 的技术论文正式发布。这篇论文不仅在技术层面具有极高的参考价值,其作者阵容同样引人注目,作者来自多家全球领先机构与企业,包括 SEMI、KLA、EVG、Meta、TSMC、HP、Google 以及 ASE。

01

台积电(TSMC)

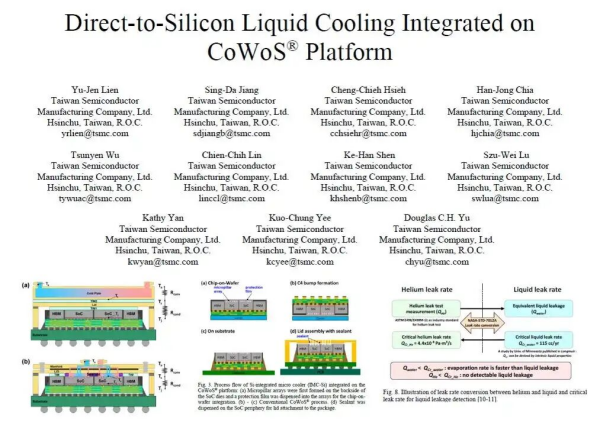

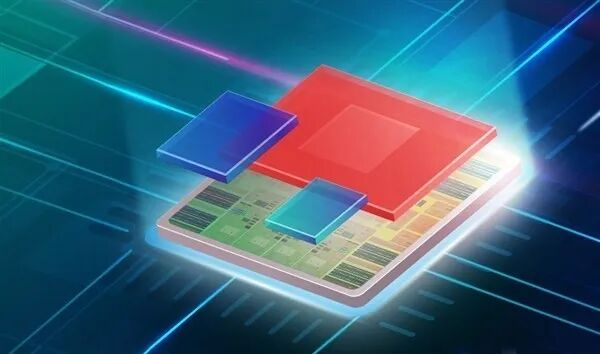

台积电在IEEE ECTC 2024 上展示了其 “硅集成微型冷却器(Si‑Integrated Micro‑Cooler)” 技术。该方案通过MEMS/DRIE 工艺,在有源芯片背面直接刻蚀晶圆级微通道结构,并与 CoWoS 封装及中介层(Interposer) 集成,能够支持高达 2.6 kW 的热负载,同时将温差控制在约63 °C。

目前台积电仍在持续推进多种微通道结构的研究,包括沟槽型、柱阵型以及平面型设计。其中柱阵型微通道结构在综合性能方面表现最优。

02

EVG(EV Group)

EVG 提供了在晶圆尺度嵌入微通道结构所必需的核心晶圆键合技术。其GEMINI 和 EVG501系统支持 最高可达 350 kN 的大面积高压力键合,这是在 SoC 与 HBM 之间集成微通道晶圆的关键能力。

03

KLA(SPTS Technologies)

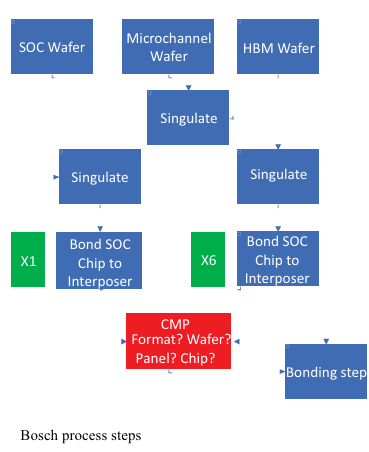

通过其子公司 SPTS Technologies,KLA 为微通道制造提供了关键的 MEMS 制程设备。其基于 Bosch 工艺的DRIE(深反应离子刻蚀)系统被公认为业内实现高深宽比结构(如深沟槽和TSV)的领先方案。这些设备对于在硅中制造可靠、一致的微通道结构至关重要。

04

HP

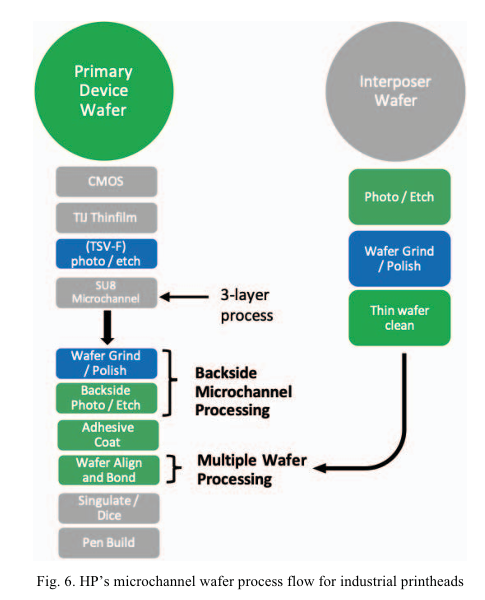

HP在基于 MEMS 的喷墨打印头制造 领域拥有长期积累,其单颗芯片上可集成数千个微流体喷嘴。这表明 HP 在 大规模背面刻蚀与流体控制表面 方面具备深厚的技术基础。尽管 HP 目前并未将芯片冷却作为其直接市场化产品方向,但其 MEMS 技术积累意味着其微流控技术具备向 先进热管理应用 延展的潜力。

05

Meta、Google、ASE

尽管 Meta 与 Google 在微通道冷却方面的具体技术细节尚未公开,但两家公司均长期参与 ECTC 以及先进封装相关的研发合作。作为全球领先的OSAT厂商,ASE(Amkor / ASE 集团) 在 晶圆到晶圆键合、中介层集成以及系统级封装 等方面具备关键能力,是微通道系统实现量产化不可或缺的参与方。

06

研究目的与产业意义

该研究的核心目标在于解决 下一代 AI 芯片所面临的热瓶颈问题,并为未来提出 具备可扩展性与可制造性的系统性解决方案。随着 AI 模型进入 万亿参数时代,单颗 SoC 的功率密度已超出传统散热模块的能力范围。无论是风冷,还是单点液冷方案,在 3D 堆叠先进封装背景下 都已难以满足需求。为应对这一挑战,研究团队提出了一种 以晶圆级微通道冷却为核心的新型热架构。

论文系统性地梳理了多项关键技术,并强调了支持该方案实现量产所需的完整产业链协作,包括:

·晶圆‑晶圆(WoW)键合:SoC 与 HBM 在晶圆层级完成键合,中间嵌入基于 MEMS 的微通道晶圆。该技术由 EVG 等领先晶圆键合设备厂商支持。

·基于 MEMS 的微通道制造:通过 深反应离子刻蚀(DRIE) 工艺,在硅晶圆中形成流体通道结构,核心设备与量测技术由 SPTS Technologies(KLA) 提供。

·系统级封装集成:SoC、HBM 与微通道晶圆被集成为单一系统,并安装于中介层之上,形成完整的 System‑in‑Package(SiP)。台积电与 ASE 等晶圆厂和 OSAT 在后段制程与热封装方面发挥关键作用。

07

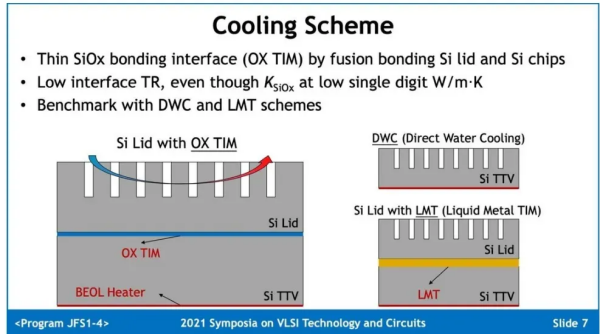

台积电的战略参与:从 TIM 挑战到 No‑TIM 架构

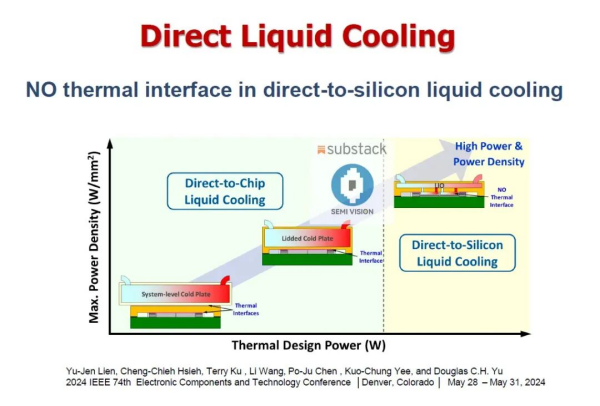

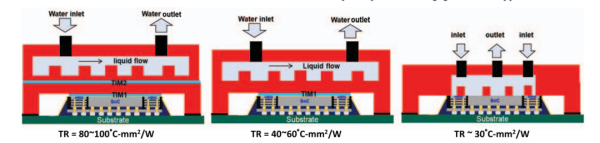

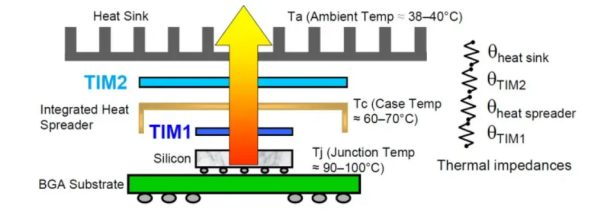

论文对长期存在的芯片热管理瓶颈——热界面材料(TIM) 的限制进行了深入分析。

传统结构如下:

AI 芯片 → TIM1 → 盖板(Lid) → TIM2 → 冷板

其中TIM1(芯片与盖板之间);TIM2(盖板与冷却模块之间)是整体热阻的重要来源。TIM 层中常见的空洞、附着不良以及接触不均匀问题,都会显著降低热性能。

为此,台积电在论文中提出了一种前瞻性的 “No‑TIM” 架构:彻底取消 TIM 层;通过结构设计,实现芯片背面与冷却结构的直接热接触;显著降低界面热阻。

这一思路也与台积电在 ECTC 其他论文中反复强调的方向一致,即 在封装层级进行热‑系统协同设计(Thermal Co‑Design)。

08

结语与技术展望

该篇论文是一次典型的跨学科、跨产业链国际协作成果。它清楚地表明未来半导体创新将不再仅由信号完整性或封装密度所定义,热架构与热协同设计 将成为同等重要的核心维度。在未来 AI 计算时代,真正的问题已不再是:

“我们还能堆叠多少芯片?”

而是:

“我们能否有效地把这些高性能芯片产生的热量散掉?”

在这一背景下System‑on‑Wafer(SoW)架构、微通道集成、No‑TIM 策略以及嵌入式液冷技术,将共同定义下一轮产业竞争的前沿。

AI芯片热管理的核心挑战今天已经集中在芯片本身。因此对于晶圆代工厂来说,从自身价值链出发提出系统性解决方案至关重要。以下内容进一步阐述这一点,重点聚焦台积电在硅基架构下的努力——尤其是在微通道冷却、DRIE/MEMS 应用、铜柱阵列设计、TIM 材料挑战以及 No-TIM 架构方面的探索。这些热管理方案不仅适用于 SoW 和 CoWoS,也适用于硅光集成先进封装。

随着人工智能计算进入万亿参数模型时代——训练功耗可达到数百千瓦,AI芯片的设计瓶颈正在从计算能力和存储墙转向另一个无形的障碍:热墙。现有主流散热技术,包括风冷和传统液冷,在处理超过300 W/cm² 的热通量时已日益不足。此外,AI 芯片上不均匀的热分布增加了热管理复杂性。传统散热结构,例如“AI 芯片 → TIM1 → 盖板 → TIM2 → 冷板”,引入了多个热界面,显著增加了热阻,限制了热传导效率和系统整体性能。

为应对这一热危机,产业正在将关注点上移:热路径设计应从先进封装和晶圆制造阶段开始,而不应仅在后段被动处理。因此本文重点探讨晶圆级集成、MEMS 制造和基于微通道液冷系统的创新,并特别关注台积电及其他领先代工厂如何引领系统级热突破。该篇文章反映了设计理念的根本转变:代工厂不再仅仅是制造者,而是 AI 芯片热管理的核心架构师。

随着3D IC、Chiplet 和 System-on-Wafer 架构时代的到来,只有在硅级嵌入热优化,才能真正突破热极限。这是封装、硅工艺工程和液冷创新交汇处的一次革命,是从“散热”到“热协同设计”的哲学进化,标志着推动 AI 未来的一次关键跃迁。