台积电(TSMC)新突破!CoWoS平台集成直接硅液冷

来源 | IEEE

链接 | https://doi.org/2377-5726/25/$31.00 ©2025 IEEE

01

为何必须突破传统散热?AI 时代的 “热困境”

当大模型的参数从百亿级跃升至万亿级,当高性能计算(HPC)在气候模拟、量子计算等领域的算力需求持续翻倍,芯片行业正面临一个比 “制程突破” 更紧迫的挑战 ——散热。按照摩尔定律,芯片晶体管密度每 18-24 个月翻倍,但如今 AI 模型的规模增长速度早已远超这一节奏。为了跟上算力需求,单纯依靠 “缩小晶体管尺寸” 的传统路径已不够,行业转向了异构集成技术,通过将逻辑芯片、高带宽内存(HBM)、加速器等不同功能的芯片 let(芯粒)通过 2.5D/3D 封装方式整合在同一中介层上。

这种设计的优势显而易见:芯片间距离从毫米级缩短到微米级,数据传输的带宽大幅提升、延迟显著降低,能效比也随之优化。比如台积电的 SoIC® 3D 堆叠技术,通过垂直方向的紧密连接,让芯片性能再上一个台阶。但问题也随之而来 ——功率密度的 “爆炸式增长”。最简单的例子:将两颗逻辑芯片垂直堆叠,功率密度会直接翻倍。而 AI 芯片的单个芯片功率已达数百瓦,多芯片集成后,整个封装的功率密度更是突破传统散热方案的极限。过去,行业主要依赖两种散热方式:

风冷:成本低但效率有限,面对高功率密度芯片时,风扇转速拉满也无法阻止芯片 “过热降频”;

间接液冷:通过冷板 + 热界面材料(TIM)传递热量,但 TIM 层、冷板与芯片的接触面会产生额外热阻,热量无法快速导出,尤其难以解决局部热点问题

数据显示间接液冷的热阻会让高功率密度芯片的散热效率损失 30% 以上,当功率密度超过 1.5W/mm² 时,甚至会出现 “热饱和”—— 无论如何提升冷却液流量,散热效果都不再改善。在这样的背景下,直硅液冷技术(Direct-to-Silicon Liquid Cooling)进入了行业视野。它的核心思路很直接:让冷却液 “跳过中间环节”,直接接触硅芯片的背面,最大化热传递效率。

但新的问题又来了,主流 HPC/AI 芯片大多采用台积电 CoWoS® 封装平台,这种平台能支持大尺寸中介层,实现多芯片的高密度互连与高带宽通信。要让直硅液冷落地,必须解决两个关键问题:如何在不改造现有 CoWoS® 产线的前提下,整合液冷结构;数据中心对 “漏液” 零容忍,如何保证长期使用中冷却液不泄漏。此前的直硅液冷方案要么忽略了与先进封装的兼容性,要么采用垫片、O 型圈等密封方式 —— 这类方案在小尺寸芯片上可行,但面对 CoWoS® 平台的大尺寸封装时,会因芯片翘曲、拓扑变化难以适配,根本无法量产。

02

成果掠影

近日,台积电通过在 CoWoS® 平台上集成 IMC-Si(硅集成微冷却器)的研究解决上述的矛盾,突破 AI/HPC 散热瓶颈。台积电首次在 3.3 倍掩模版 CoWoS®-R 平台集成直硅液冷方案(IMC-Si),仅需微调现有 CoWoS® 工艺即可兼容量产需求,且弹性密封胶能适配大尺寸封装160-190μm的翘曲问题。

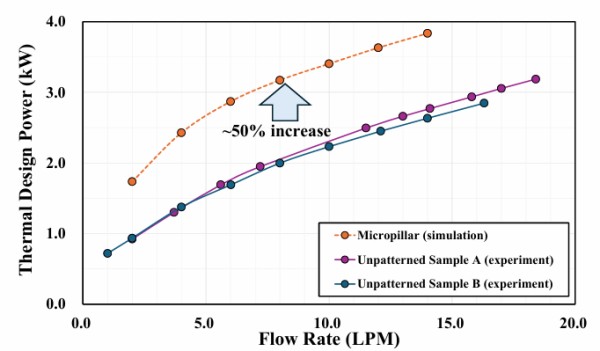

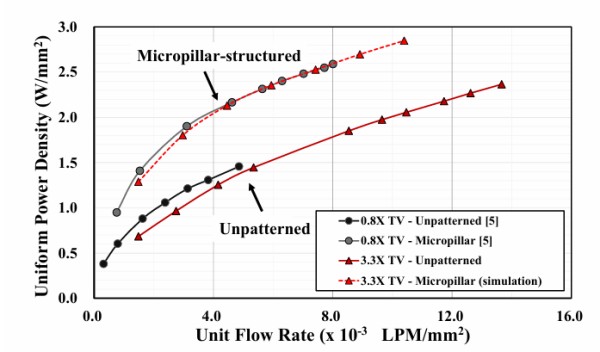

以 40℃纯水为冷却液、流量 10LPM 时,可实现 3.4kW 总散热功率(1.6 倍掩模版 SoC 功率密度达 2.5W/mm²),无微粒阵列方案在 11.5LPM 流量下也能实现 2.5kW 散热(1.9W/mm² 功率密度),且芯片背面微柱阵列通过增加散热面积和诱导湍流,能额外提升 50% 散热效率,同时从 0.8 倍掩模版单芯片扩展到 3.3 倍掩模版 CoWoS® 平台时,IMC-Si 散热能力保持稳定(如单位流量 5×10⁻³ LPM/mm² 时,两者功率密度均约 1.5W/mm²);

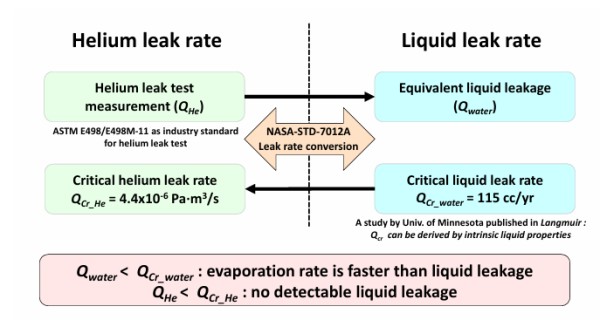

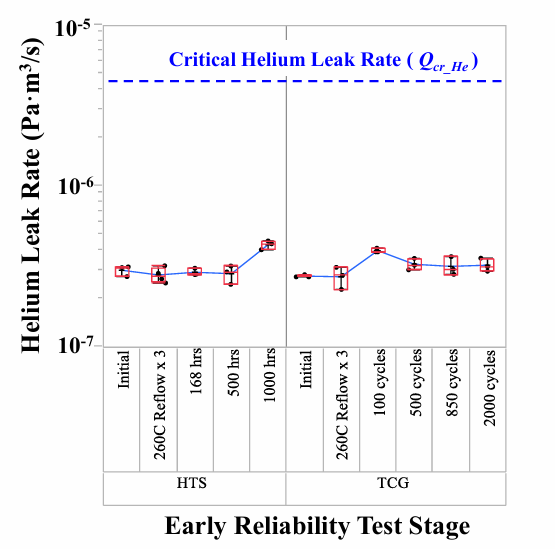

参考 OCP 和 NASA-STD-7012A 标准定义临界漏率,集成系统通过3次回流焊(260℃)、2000 次温度循环(-40℃至 125℃)、1000 小时高温存储(150℃)及 1000 小时高温高压液浸(150℃、4.8bar)测试,氦气漏率始终比临界值低一个数量级,无漏液风险,且密封胶在温度波动和长期热机械应力下未分层。

该技术为 AI/HPC 芯片提供可量产的散热方案,奠定未来数据中心部署基础,后续还将通过优化微柱设计和缓解翘曲进一步提升效率。研究成果“Direct-to-Silicon Liquid Cooling Integrated on CoWoS® Platform”为题发表在《IEEE》

03

图文导读

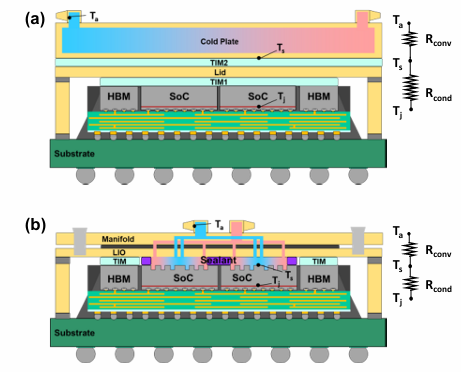

图 1:(a) 传统 CoWoS® 封装,包含热界面材料(TIM1 和 TIM2)及盖板,盖板将硅芯片与冷却液隔开;多重界面增加了热阻,限制了冷板对热点热量的散出能力。(b) 集成式直硅液冷结构,硅芯片背面蚀刻有微柱阵列,盖板通过密封胶与封装连接;冷却液与硅芯片之间无间隔,可实现更高热流密度的散热。

图1对比传统散热与直硅液冷两种方案的结构差异及散热能力差距;传统 CoWoS® 封装的间接液冷结构:该结构中,硅芯片与冷却液之间存在热界面材料(TIM1、TIM2)和盖板两层间隔。TIM 层虽用于填充芯片与盖板的缝隙,但会引入额外热阻,且多层界面叠加进一步增加热传递阻力,最终导致冷板无法高效散出芯片热点的热量,尤其在高功率密度场景下(如 AI/HPC 芯片),散热效率会大幅受限。

集成直硅液冷的结构去掉了TIM层和盖板的间隔,直接在硅芯片背面蚀刻微柱阵列(增大散热面积),并通过密封胶将盖板与封装连接,形成防漏腔室。冷却液可直接接触硅芯片背面,无中间界面阻碍热传递,能突破传统方案的热流密度限制,实现更高功率的散热,精准解决高功率密度芯片的散热痛点。

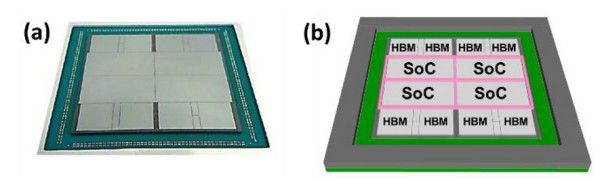

图 2:(a) 3.3 倍掩模版尺寸的 CoWoS®-R 热测试载体(TTV),集成了电阻温度探测器(RTD)和加热器。(b) 3.3 倍掩模版尺寸 CoWoS®-R 热测试载体(TTV)的示意图,密封胶位置以粉色标注。

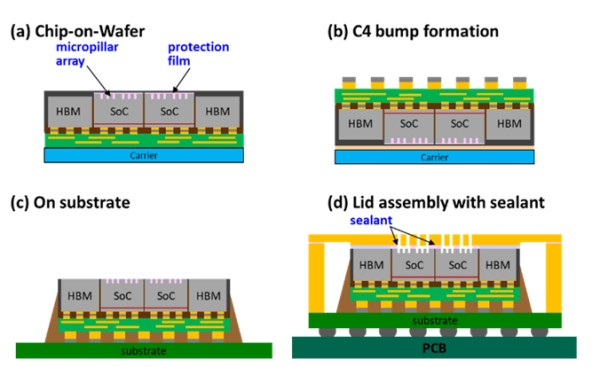

图 3:硅集成微冷却器(IMC-Si)在 CoWoS® 平台上的集成工艺流程:(a) 首先在 SoC 芯片背面制作微柱阵列,并在阵列中涂覆保护膜,用于芯片 - 晶圆集成;(b)-(c) 传统 CoWoS® 工艺流程;(d) 在 SoC 芯片外围涂覆密封胶,用于盖板与封装的连接。

图清晰展示硅集成微冷却器(IMC-Si)在 CoWoS® 平台上的集成工艺流程,凸显该方案 “仅需微调现有工艺即可兼容量产” 的核心优势,流程分为 4 个关键步骤:

(a) 芯片背面预处理:先在 SoC 芯片背面蚀刻出微柱阵列(用于后续提升散热面积),再向阵列中涂覆一层保护膜 —— 该膜能适配传统 CoWoS®-R 工艺的热预算,且后续可无残留移除,避免影响后续流程;

(b)-(c) 传统 CoWoS® 工艺:沿用现有成熟的 CoWoS® 封装流程,无需额外改造核心步骤,降低技术落地的工艺成本与难度;

(d) 密封与盖板组装:在每个 SoC 芯片的外围涂覆弹性密封胶,再安装带有多个进出口的盖板(进出口与每个 SoC 的冷却腔室对齐)—— 密封胶采用 “1D 线条式” 涂覆(而非覆盖整个芯片表面),可适配大尺寸封装的翘曲问题,同时保证盖板与芯片的紧密接触,为后续防漏液奠定基础。

整个流程仅新增 “微柱阵列制作 + 保护膜涂覆 + 密封胶涂覆”3 个简单步骤,充分体现了方案对现有 CoWoS® 产线的兼容性,是实现量产的关键设计。

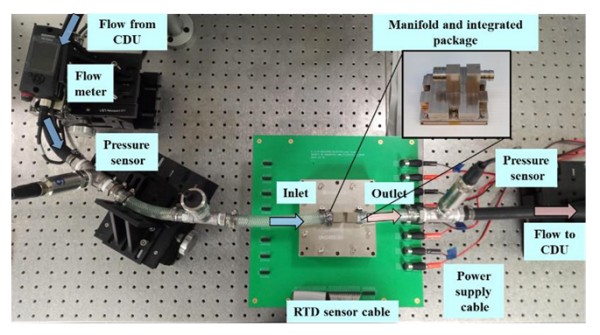

图 4:热特性表征实验装置。

图 5:3.3 倍掩模版尺寸 CoWoS®-R 封装上硅集成微冷却器(IMC-Si)的热特性表征结果:无图案(未蚀刻微柱阵列)的 SoC 芯片可实现超过 3kW 的散热功率,而带有图案化微柱阵列的 SoC 芯片可额外获得 50% 的散热增益。

图 6:不同测试载体(TV)上硅集成微冷却器(IMC-Si)的热性能对比,数据基于散热设计功率(TDP)和流量按加热面积归一化;结果表明,从 0.8 倍掩模版单芯片扩展到 3.3 倍掩模版 CoWoS® 封装时,IMC-Si 的散热能力保持稳定。

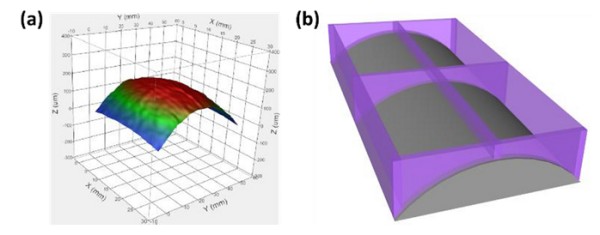

图 7:(a) 4 颗 SoC 芯片的实验性拓扑图,显示总翘曲量为 160-190 微米(μm)。(b) 4 颗 SoC 芯片及密封胶的示意图;沿密封胶的中心垂直线处,硅芯片与盖板之间的间隙最小,因此散热效率最高,但液体流动阻力也最大。

图 8:氦气泄漏率与液体泄漏率的换算关系及液体泄漏检测临界泄漏率示意图。

图 9:集成硅集成微冷却器(IMC-Si)的 3.3 倍掩模版尺寸 CoWoS®-R 封装的氦气泄漏率变化图;结果显示,在长达 1000 小时的高温存储(HTS)和 2000 次的温度循环(TCG)测试中,封装的氦气泄漏率始终保持稳定,且比临界泄漏率低一个数量级,可防止液体积聚。