韩国科学院芯片 “散热” 综述,关键技术、表征方法与未来方向

来源 | Microelectronics Reliability

链接 | https://doi.org/10.1016/j.microrel.2025.115782

01

背景介绍——芯片 “退烧” 有多难?

在半导体行业的发展历程中,芯片性能曾沿着摩尔定律稳步提升 —— 每 24 个月,芯片上的晶体管数量便实现翻倍,这一规律支撑了半个多世纪以来电子设备性能的飞跃。然而,2016 年半导体行业正式宣告摩尔定律走向终结,一个长期被性能提升掩盖的核心难题逐渐成为制约行业发展的关键:芯片散热。随着芯片架构复杂度持续飙升,从传统平面设计到多芯粒集成,器件运行时单位面积产生的热量呈指数级增长,这些热量若无法及时、高效地消散,不仅会导致芯片主频被迫降低、性能大幅缩水,还会加速器件老化,严重损害长期可靠性,甚至引发瞬时故障,对航空航天、汽车电子、高性能计算等关键领域的设备安全构成威胁。

半导体封装技术正经历革命性变革,从传统的单一芯片封装向异构集成(HI)、3D 封装等先进方向快速演进。在这些新型封装结构中,CPU、GPU、内存(RAM)、传感器等多个功能芯粒被高度集成到单一封装体内,形成功能密集的 “芯片系统”。这种集成方式虽大幅提升了设备的性能密度与空间利用率,却也带来了严峻的热干扰问题 ——CPU、GPU 等逻辑运算部件作为主要热源,其产生的高温会通过封装内部的介质直接传导至邻近的内存、传感器等对温度敏感的部件,导致这些部件的工作稳定性下降,进而影响整个电子设备的运行效率与数据处理精度。例如,在 3D 堆叠封装中,上层芯片的热量若无法向下有效传递,会在层间形成 “热孤岛”,使得整体系统的散热效率远低于单一芯片封装。

更具挑战性的是,为满足 5G、人工智能、云计算等领域对高带宽、低延迟的需求,封装的互连密度正不断突破极限。数据显示,传统倒装芯片球栅阵列(FCBGA)的互连密度约为每毫米 48 个 I/O,而当前主流的硅中介层封装,其互连密度已超过每毫米 1000 个 I/O。高密度的互连结构带来了多重散热难题:一方面,密集的金属互连线路会导致电流集中,进一步加剧局部发热;另一方面,部件间的间隙被大幅压缩,散热通道变得极为狭窄,热量难以通过对流或辐射方式扩散。更关键的是,互连密度的提升会显著降低不同部件间的界面热导(ITC)—— 界面热导是衡量热量在两种不同材料界面间传递效率的核心指标,界面热导越低,热量越容易在界面处 “堆积”,形成局部高温区域,这一问题在芯片与散热部件的连接界面处尤为突出。

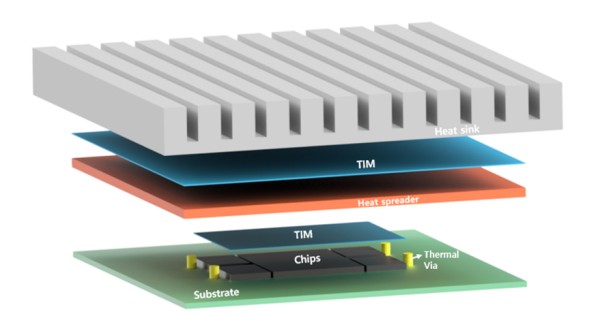

从芯片内部产生的热量,需要依次穿过封装基板、热界面材料(TIM)、散热片等多个部件,最终通过散热器传递到外部环境,这一过程中任何一个环节的热阻过高,都会导致整体散热效率下降。因此,半导体封装的热设计不再是单一部件的优化,而是需要从 “芯片到散热器” 的全链路考量:既要选择高导热性能的材料(如高导热的 TIM、散热片与基板),又要通过界面工程优化不同材料间的连接状态,减少界面热阻;同时,还需在封装结构设计中融入热过孔等主动散热结构,为热量传递开辟 “捷径”。如何平衡材料的导热性能与机械可靠性(如热膨胀系数匹配)、电气性能(如低介损),如何突破全链路散热瓶颈,已成为研发人员亟待解决的核心课题,也是推动高性能、高密度半导体系统向更高性能、更小尺寸发展的关键所在。

02

成果掠影

近日,韩国科学技术研究院Joon Sang Kang团队 “从芯片到散热器” 的全链路散热需求,系统梳理了先进半导体封装热管理的关键技术成果,为高性能、高密度电子设备的热设计提供了全面参考。

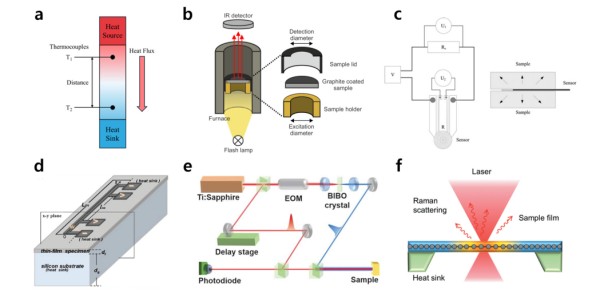

在热表征技术方面,研究明确了精准测量热导率是优化散热设计的基础。针对不同尺度封装材料,文章分类介绍了先进测量方法:对于块体材料,稳态法凭借无需复杂系统的优势,可直接测量导热膏、氮化铝陶瓷等材料的热导率,但需真空环境与规则样品;激光闪射分析(LFA)与瞬态平面热源法(TPS)则实现了快速、非破坏性测量,其中 LFA 适用于金属、陶瓷等材料的热扩散率分析,TPS 成本更低且能覆盖 0.005-500 W/m・K 的宽测量范围。针对微尺度样品,3ω 法可在 30-1000 K 温度区间测量硅、氮化镓等薄膜的热导率,时域热反射(TDTR)法则突破纳米级测量限制,能评估多层界面的界面热导(ITC),拉曼测温法则无需金属 transducer,适用于石墨烯、氮化硼等二维材料的面内热导率分析。

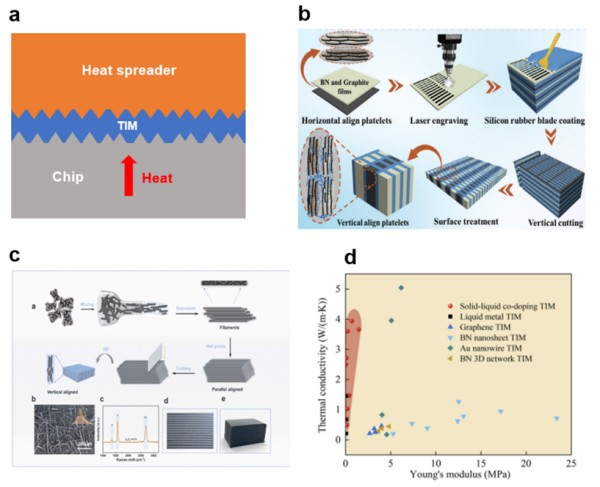

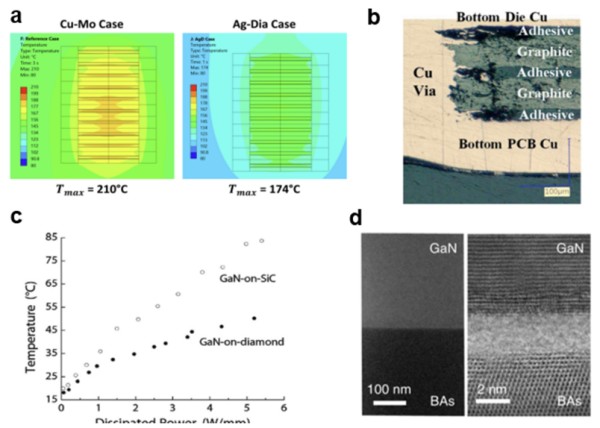

在核心热管理部件创新上,研究聚焦材料与结构优化,实现散热性能与多维度需求的平衡。热界面材料(TIM)通过垂直排列氮化硼、碳纳米管等高导热填料,结合液态金属共掺杂、耦合剂增强界面结合等策略,在提升热导率(最高达 23.7 W/mK)的同时,将弹性模量降至 2.62 MPa,兼顾柔性与散热;散热片方面,银 - 金刚石复合材料、碳化硅、金刚石等材料的应用,既实现了 800 W/mK 以上的高导热率,又通过匹配芯片热膨胀系数(CTE)减少热应力,如银 - 金刚石散热片可使封装最高温度从 210℃降至 174℃;封装基板则通过有机材料添加氮化硼纳米管、陶瓷材料优化晶粒结构等方式,在提升热导率(如 γ-Si₃N₄室温热导率超 250 W/mK)的同时,满足低介损、高机械强度需求;热过孔技术通过硅通孔(TSV)、玻璃中介层铜过孔等结构,直接构建芯片到散热器的散热通道,如单壁碳纳米管 TSV 可使芯片温度降低 38%,144 个铜过孔阵列能将玻璃中介层热导率从 1 W/mK 提升至 20 W/mK。

在界面热传输优化领域,研究提出多种创新策略以降低界面热阻。通过氧等离子体处理金属表面提升润湿性、化学机械抛光减少晶圆粗糙度,可显著提升界面接触面积与 ITC;自组装单分子层(SAM)能通过增强界面结合力、匹配声子谱,将 MoS₂/SiO₂、聚苯乙烯 / 硅等界面的 ITC 提升 2-5 倍;在 GaN 与 SiC、金刚石等材料间插入氮化铝(AlN)、AlₓGa₁₋ₓN 作为 “声子桥”,可利用中间材料的晶格与热特性,减少声子色散差异,使 ITC 提升 45%-55%;此外,硅表面构建鳍状结构增加接触面积,也能将铝 - 硅界面的 ITC 提升 88%。

未来研究将重点突破成本与可靠性平衡及定制化解决方案两大方向:一方面,需在保证高导热性能的前提下,降低新型材料(如金刚石复合材料)与工艺(如低温烧结银)的成本,同时验证长期使用中的机械与热稳定性;另一方面,针对高频通信、大功率器件等不同应用场景,研发适配其特殊需求(如耐高温、低信号干扰)的热管理方案,推动先进封装热管理技术的商业化落地与行业应用。研究成果以“A review in thermal management for advanced chip packaging from chip to heat sink”为题发表在《Microelectronics Reliability》期刊。

03

图文导读

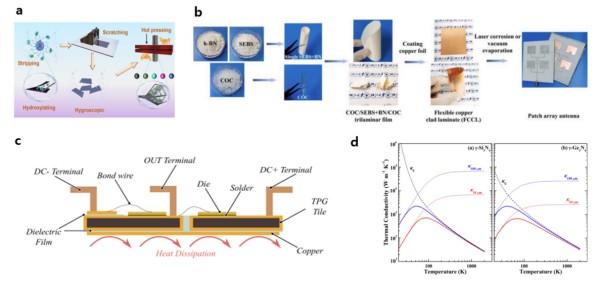

图1.典型封装结构及关键热管理部件示意图。

图2. 热导率测量技术 a) 稳态法;b) 激光闪射分析法;c) 瞬态平面热源法;d) 3ω 法;e) 时域热反射法;f) 拉曼测温法。

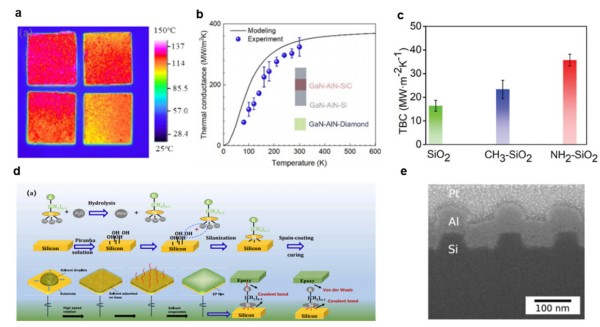

图3. 热界面材料(TIM)的热性能与力学性能。(a) 芯片与散热片之间热界面材料的结构示意图;(b) 聚合物基体中垂直排列的氮化硼;(c) 碳纤维基热界面材料的制备流程;(d) 固液共掺杂热界面材料与基准热界面材料的热导率对比。

图4.高导热率散热片。(a) 采用铜 - 钼(Cu-Mo)与银 - 金刚石(Ag-Dia)散热片的封装温度分布;(b) 印刷电路板(PCB)内部石墨散热片的结构示意图;(c) 基于碳化硅(SiC)与金刚石散热片的氮化镓(GaN)器件温度对比;(d) 砷化硼(BAs)散热片上的氮化镓高电子迁移率晶体管(GaN HEMT)结构。

图5.导热半导体封装基板。(a) 复合材料基板的制备流程示意图;(b) 高导热率环烯烃共聚物 / 苯乙烯 - 乙烯 - 丁烯 - 苯乙烯嵌段共聚物 + 氮化硼 / 环烯烃共聚物(COC/SEBS+BN/COC)夹层结构基板的制备过程;(c) 多层直接键合铜(DBC)基板的结构示意图;(d) γ- 氮化硅(γ-Si₃N₄)与 γ- 氮化锗(γ-Ge₃N₄)基板的热导率对比。

图 6. 增强界面热传输的界面工程技术。(a) 不同镍(Ni)表面处理对应的四种界面热导(ITC)值下,封装模块的表面温度图像,已获得使用许可);(b) 氮化镓(GaN)与氮化铝(AlN)之间界面热导(ITC)的实验测量结果;(c) 采用自组装单分子层(SAM)进行界面工程的封装结构示意图;(d) 环氧树脂基体与硅(Si)填料之间形成自组装单分子层(SAM)的过程;(e) 硅表面鳍状结构的扫描电子显微镜(SEM)图像。

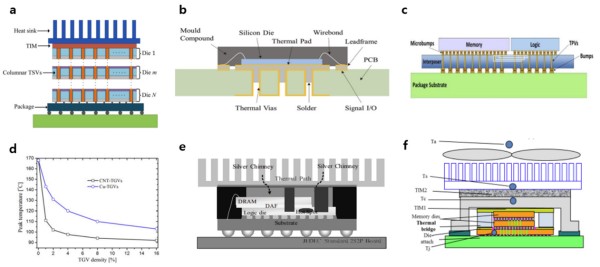

图7. 基于热过孔的热管理设计与性能。(a) 采用硅通孔(TSV)作为热过孔的堆叠芯片结构(参考文献 [152]);(b) 带热过孔的四方扁平无引脚(QFN)封装在印刷电路板(PCB)上的结构示意图;(c) 含贯通封装过孔(TPV)的 2.5D 玻璃中介层结构示意图;(d) 玻璃中介层上芯片的峰值温度随热过孔密度变化的关系曲线(引用自 IEEE 期刊文献 [155],已获得使用许可);(e) 带热通道(Thermal Chimney)的系统级封装(SiP)芯片结构示意图;(f) 带热桥(Thermal Bridge)的 3D 封装结构示意图。