数据中心热得发烫?问题出在芯片这头

提起数据中心散热,很多人以为这是一个统一的问题

只需要一套方案从芯片到机房一路打通

但事实上,行业早已天然分成两拨人

两拨人思维模型不同,话语体系不同,连“散热”的定义可能都不一样

可问题是——当芯片热管理无法与系统级设计对齐

谁来负责系统真正的热效率?谁来接住芯片的“热浪”?

这之间,又该如何打通?

00

关于“引言”

当前我们谈论“数据中心热管理”的时候,其实可以分为两个阵营:

阵营一:做芯片热管理的专注局部高热通量(几百到上千W/cm²)关注微尺度仿真、界面热阻、TIM、微通道、TSV结构、先进封装等等;最怕遇到热堆积、界面失效、封装不匹配等等问题。

阵营二:做系统/机房热管理的面对的是大尺度、多节点散热,更关注液冷CDU、流量匹配、风道设计、冷热通道隔离、PUE,IDC运营商、云厂商、集成商;最怕遇到PUE失控、系统不稳定、部署难落地等等问题。

两拨人虽然都在谈“热管理”,但讲的却是完全不同的语言,也解决着完全不同的问题。

“数据中心散热不就是装个冷板、建个冷通道?”在一些做系统级散热的工程师眼里,芯片级热管理似乎只是一个“接口问题”,而在芯片热管理圈子里,另一种声音是:“我们在几毫米范围内解决的是几百W/cm²的热源,真正难的活,已经在芯片层面干完了。”芯片热管理是散热系统的基础,也有被被孤立于上层系统设计之外。想真正优化数据中心PUE和系统稳定性,必须从协同做起。真正的挑战,如何将这两套体系如何打通,构建一个协同的、系统级的热管理闭环。

本文,小编先从芯片热管理出发,看看这一层里到底有哪些技术挑战、材料创新与产业卡点,也试着解答一些关键问题。下一篇,我们将沿着热传导路径,探讨“服务器级”与“机房级”的热管理方法,看看服务器/机房级热管理如何接住芯片的“热浪”。

01

热,从芯片开始

数据中心的热管理之争,归根结底,都始于芯片本身的发热。芯片不再是“冰冷”的运算器件,它正以每代翻倍的方式,把热量堆积到毫米尺度的硅片上。这一节,我们从热的源头——芯片结构、制造工艺与封装架构——出发,看看散热难题到底是如何一步步被“写死”的。

从一颗芯片的诞生,我们能看到芯片级热管理的复杂度——尤其是像英伟达GB200这样“热得惊人”的算力怪兽。

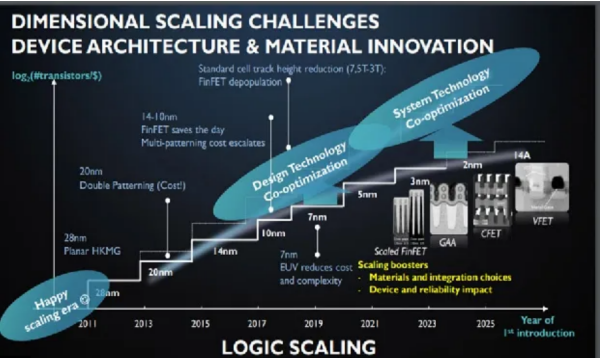

1.1 高热通量,是从制程阶段“写死”的

芯片的高热通量,早在制程节点的演进中就埋下了伏笔。随着晶体管尺寸从7nm、5nm、一路向3nm推进,虽然单个晶体管的功耗下降,但集成密度大幅提升,整体功耗反而不断上升——等效于在一张邮票大小的区域里堆上了数百瓦、甚至上千瓦的热量。单位面积的热流密度轻松突破数百W/cm²,某些AI大芯片甚至达到1000W/cm²以上的热密度。

更让人头疼的是,热并不是均匀分布的,而是“孤岛式”集中在几个高功耗模块上。这种非均匀性导致传统的热扩散手段效果极差,“局部过热”成了芯片热管理的第一拦路虎。

芯片制程变化

4月29日2025英特尔代工大会(Intel Foundry Direct Connect)上,英特尔CEO陈立武公布最新制程工艺技术路线图,计划今年年内量产Intel 18A(1.8nm),2026年推出Intel 18A-P节点以及与联电合作的12nm制程工艺,2027年推出Intel 14A及其变体Intel 14A-E,2028年推出Intel 18A-PT制程,并首次披露先进节点Intel 14A(1.4nm)的详细规格。

2025英特尔代工制程路线。图源:芯东西

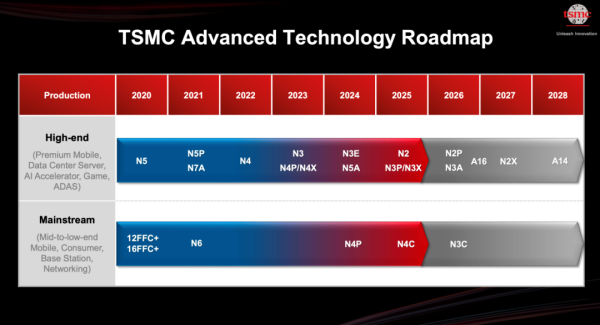

近日台积电在美国举办了tsmc symposium 2025,会上他们发布了一系列新技术,并对路线图做了更新。值得一提的是,公司第二代GAA工艺14A也首次曝光。台积电的N3系列(即3nm工艺)已包含已量产的N3和N3E,并计划后续推出N3P、N3X、N3A以及N3C等版本。

2025TSMC制程路线。图源:锐芯闻

1.2 封装结构,把热路径变得更复杂

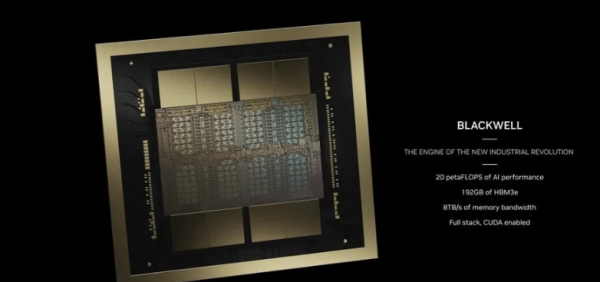

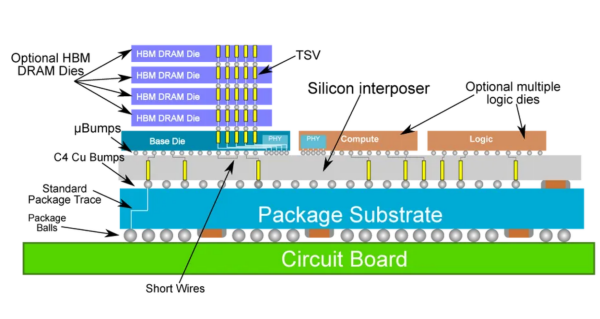

当芯片制造完成,它被封装成器件,热管理的难题才刚刚开始。现代高性能芯片,早已不满足于单芯片封装,它们需要把多个Die堆叠、集成、互联,构建复杂的异构系统。以NVIDIA最新的GB200系列为例,其B200芯片采用了台积电的CoWoS封装技术,集成了多个H100/B100逻辑Die与HBM堆栈。

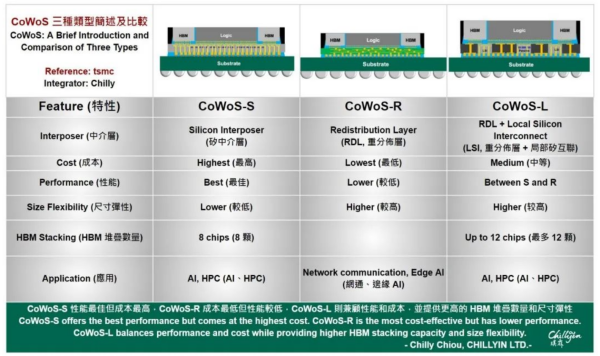

CoWoS由CoW和oS组合而来:先将芯片通过Chip on Wafer(CoW)封装制程连接至硅晶圆,再把CoW芯片与基板(Substrate)连接整合成CoWoS。(CoWoS目前可以分为CoWoS-S/CoWoS-R/CoWoS-L三类工艺类型,三种工艺之间的区别是介质层的不同,其中S是硅中介层、R是重分布层、L是重分布层+局部互联)。

CoWoS将不同功能的芯片(如CPU、GPU、HBM芯片等)集成到一个封装中,这些芯片可以采用不同的制造工艺节点,从而实现最佳的性能和成本效益组合。核心是将不同的芯片堆叠在同一片硅中介层实现多颗芯片互联。在硅中介层中,台积电使用微凸块(μBmps)、硅通孔(TSV)等技术,代替了传统引线键合用于裸片间连接,大大提高了互联密度以及数据传输带宽。多芯片集成的封装需要有效的散热管理,CoWoS技术通过优化的封装设计和材料选择,可以实现高效散热,从而确保芯片在高负载下稳定运行。

CoWoS结构。图源:科技前线阵地

CoWoS-S/R/L结构。图源:锐新闻

这些先进封装的特点是:

多层堆叠结构(例如TSV + HBM堆栈);

多芯片系统级集成(如Chiplet架构);

更小的热通道、更长的热路径;

多种材料界面(硅、铜、TIM、封装基板……)组成复杂热阻网络;

热在这些路径中被反复折射、阻滞,每一层的材料变化、每一次结构过渡,都是一个潜在的“热阻塞点”。而在微观层面,“界面热阻”成为决定热管理成败的关键因素之一。一旦TIM失效或材料膨胀系数失配,轻则热阻增大,重则直接导致封装层剥离、失效。简而言之,先进封装虽然带来了更高的计算密度,但也让热更难“走出去”。

1.3 瞬时响应,才是更难的挑战

芯片不是恒功率设备。特别是AI芯片和高性能CPU,其运行状态高度依赖任务负载,在毫秒级甚至微秒级别上,热量会突然攀升。以大模型推理为例,芯片在短时间内会经历“功耗脉冲”——几十W到几百W的瞬时跳变。这种动态工况需要极强的瞬态热响应能力,而不是“常温下慢慢散”。热一旦管不好,不只是“降频”那么简单。HBM过热会影响带宽,TSV区域过热可能引发封装翘曲或界面失效,甚至加速芯片老化寿命缩短。

传统散热系统(风冷、冷板)设计多基于稳态热阻模型,而现实中,瞬态热冲击才是真正能压垮芯片稳定性的根源。这也是近年来微热管、微通道冷却结构、甚至TSV内集成液体散热等“近芯片冷却”方案被重新审视的原因。

散热的第一公里,始于芯片,又止于芯片。

02

芯片级热管理解决方案

如果说芯片是一座正在全速燃烧的“算力引擎”,那么芯片级热管理就是负责在几毫米尺度里“导走热量、疏通瓶颈”的前线工程。

这一层的挑战,是最“精细化”的散热任务。 它既要与先进封装结构兼容,又要在极小空间内控制热阻,还要经得起反复热循环与可靠性测试。在AI芯片功耗动辄几百瓦的时代,芯片热管理已经不是“贴个散热片”就能解决的问题了。

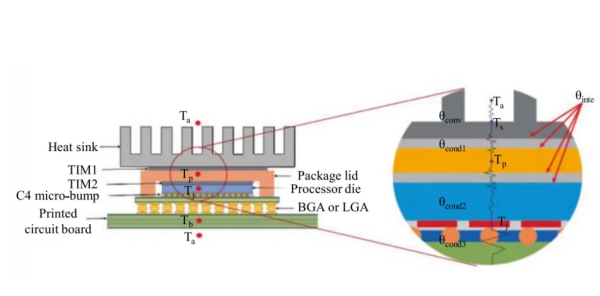

2.1 芯片散热结构简析

芯片散热是将芯片晶片产生的热量通过三种传热方式传递给外界环境。热传导和热对流在芯片散热中起主要作用,而辐射可以忽略不计。下图展示出一种传统倒装芯片的封装结构和风冷散热途径。裸芯片的有源区域使用焊料凸点反向连接到基板。封装外壳必须位于裸芯片上方,以确保机械强度并减轻环境影响。为了使接触热阻最小化,需要在两个界面之间填充热界面材料(TIM)。热量在芯上产生,然后通过多层封装和TIM从进行传导,随后到达芯片表面,通过热对流传递到冷却介质中。空气冷却的对流换热系数相对较小,约为10 ~ 100 W/(m2⋅K),需要100 ~ 1000℃的温差才能达到1 W/cm2的热流密度。为了获得高热流密度,在芯片顶部安装散热器是一种常见的做法,以增加传热面积。

传统封装结构中芯片的散热路径。

来自芯片的热量散发到芯片上下的周围空气中。在芯片上方,热量从芯片传递到封装外壳,然后从封装外壳传递到外部空气。这条通路涉及三个热阻:从晶体管到外壳的导热热阻,从外壳到散热器表面的热阻,以及散热器与外界环境之间的对流换热热阻。在芯片下面,热量从芯片传递到印刷电路板,然后从印刷电路板传递到外部空气。

2.2 热界面材料(TIM):热通道的第一公里

热从芯片内核出来,首先遇到的是封装结构和冷却结构之间的界面热阻。这层薄薄的接触面,往往是整个散热路径中“阻力最大”的一环。TIM的作用,就是填满芯片与冷却结构之间的微小缝隙,提升热传导效率。

常见方案:

导热硅脂:成本低、填充性好,但高温下容易泵出、干涸;

相变材料(PCM):接触时自动软化填充,热阻更小,但热稳定性仍是挑战;

金属TIM(如液态金属、钎焊):

针对高热通量芯片;

接触热阻极低,但对工艺要求高,可靠性考验大;

弹性金属垫片(如铟片):兼顾导热与可靠性,常用于定制高端封装。

技术趋势: 多数厂商正在从“导热率高”转向“界面稳定性更高”的材料选择——尤其是在大封装、长生命周期的芯片场景里,界面可靠性比初始性能更重要。

NVIDIA H100 在封装中使用了相变材料+液态金属TIM的混合策略。在高热通量区域(如GPU die正上方)采用液态金属,以确保极低热阻;而在次级接触区域采用高性能PCM材料,兼顾填隙性和长期稳定性。在超过700 W/cm²的热流密度下,依然能够保持主热源区域的稳定工作温度,延长芯片可靠寿命。

2.3 封装热设计:从结构到材料的热协同

随着AI芯片走向大面积、高功耗、多芯粒(如 NVIDIA 的 GB200),封装本身就成了热管理的一部分,热不再只是“芯片出来以后的问题”。芯片封装不再是一个“盒子”,而是一个带热结构的“热载体”。

几个关键词你可能已经听说:

TSV(硅通孔)+ RDL(再布线层):为3D芯片封装导热提供垂直路径;

CoWoS、Foveros、EMIB 等先进封装:芯片堆叠、异构集成更复杂,对热路径设计提出挑战;

硅中介层(interposer):除了电连接,也成了导热通道;

盖板(lid)+底部填充材料(underfill):结构强度与热阻控制二者都要。

趋势关键词:“热封装协同设计”。热管理不再是封装完成之后再来“补救”,而是在结构设计初期就考虑热路径布设。最典型的就是:封装内嵌冷却结构;热扩展层设计(如石墨散热层);双面散热(上下表面同时接触冷却结构)。

Ponte Vecchio 是Intel为高性能计算设计的多芯粒GPU封装,采用了 EMIB + Foveros 的异构集成结构。为了降低热阻,Intel特别开发了散热中介层(Thermal Bridge),连接多个die之间的热扩展结构,并使用钎焊封盖(soldered lid)+局部液冷方案,提前布局热路径。封装本身不仅电连接,也成了“热扩散骨架”,多达47颗chiplet在封装内热传导路径优化极致。

2.4 冷却结构演进:微通道与封装内液冷

过去十年,芯片冷却结构大致从“散热片+风冷” → “冷板+液冷” → “微通道+定制液冷”三阶段演化。在AI芯片时代,散热结构正朝着“更靠近热源”发展的趋势演进。

1)微通道冷却(Microchannel Cooling)

把冷却液体直接引入带有数百个微细通道的冷却腔室中;

通道越细,换热面积越大,热阻越低;

但设计难点是压降控制、堵塞风险、制造成本高。

2)封装内液冷(In-Package Liquid Cooling)

把冷却结构直接做到芯片封装内部,热路径极短;

例如Intel在OneAPI平台上展示的异构芯片内冷却方案;

对封装工艺、材料密封性要求极高,仍处在研发/定制阶段。

3)双面冷却(Double-Sided Cooling)

AI芯片的封装越来越“立体化”,双面同时散热成为高效路径;

AMD、TSMC均在3D封装项目中使用双面冷却结构。

IBM 在Power9的AI加速节点(如AC922服务器)上引入了chip-level direct-to-chip液冷方案,其核心是定制微通道冷板贴合CPU和GPU die表面。 该方案可实现单芯片超过300 W的散热能力,温度波动控制在±1°C以内,是芯片级液冷在商用HPC中的早期标杆。

2.5 材料创新:热管理从“导热材料”变成“热系统材料”

传统上,芯片热管理材料就是导热填料、导热垫片这些“被动”材料。但在今天,材料已经开始走向“结构功能一体化”。

典型趋势包括:

高导热陶瓷(AlN、SiC)基板代替传统有机基板;

液态金属+高分子复合,做成柔性高导热接口材料;

超薄石墨膜、碳纳米管阵列,用在芯片层内构建散热结构;

电磁屏蔽 + 散热一体化材料,适配5G/AI SoC多目标需求。

材料的方向不只是更“能导热”,而是更能适应微米尺度上的热传导协同,更能匹

配封装机械要求、热膨胀系数,甚至能参与冷却液接触。TSMC在其CoWoS-R封装平台中,逐步引入了高导热陶瓷复合基板(疑似采用AlN或高热SiO₂复合材料),用以替代传统有机BT基板,面向NVIDIA H200、AMD MI300等高热密AI芯片,TSMC正在将热管理与基板材料协同设计。

整体来看芯片热管理的研究方向主要围绕的是降低接触热阻、新型TIM材料的开发、针对热点的管控、散热技术、先进封装、温度感知及预测及全链路热管理的优化等等不同方向。当前产生一系列芯片冷却技术,包括风冷、 冷板式液冷、微通道冷却、浸没式冷却、热管冷却、射流冲击、喷雾冷却、热电冷却、电热冷却等。

03

最后

从材料到结构,从接口到通道,芯片级热管理正在以“毫米级”的精度挑战着瓦级的热源密度。面对持续上升的热流密度,任何一处热阻、任何一层材料、任何一个结构设计失误,都会成为整机散热系统的“堵点”。而所有这些“微观散热战”,最终都是为了解决一个问题——如何不让热拖累算力。但局部最优 ≠ 全局最优。

芯片级再精妙的热管理,如果与系统级的冷却方案不匹配,热量一样“走不出去”。